ThinkingMachineの後はASCIに……と思ったが、その前にもう少し超並列マシンの系譜を解説したい。今回はその1つ目、インテルのiPSCだ。これはインテルのTouchstoneやParagonにつながるシステムである。

Paragonの話は、連載116回で少しだけ触れた事があるが、まずは順を追って説明したい。

iPSC/1。画像はComputer History Museumより

インテル製の超並列マシンiPSC/1

売れ行きはそこそこ

1984年、米Oregon州にあるBeavertonにインテルはScientific Computers Group(SCG)という部隊を作る。このBeavertonは、D1C/D1XといったインテルのMother FabがあるHillsboroに隣接しており、実際D1C/D1XがあるRonler Acres Canpasのすぐ隣りと思えばいい。

このSCGのマネージャーはインテルの前CTO(現在はSenior Fellowのポジションで休職中)だったJustin Rattner氏であった。SCGはその後、Supercomputer Systems DivisionやScalable Systems Division(どちらもSSD)と名前を変えるが、それはあまり重要ではない。

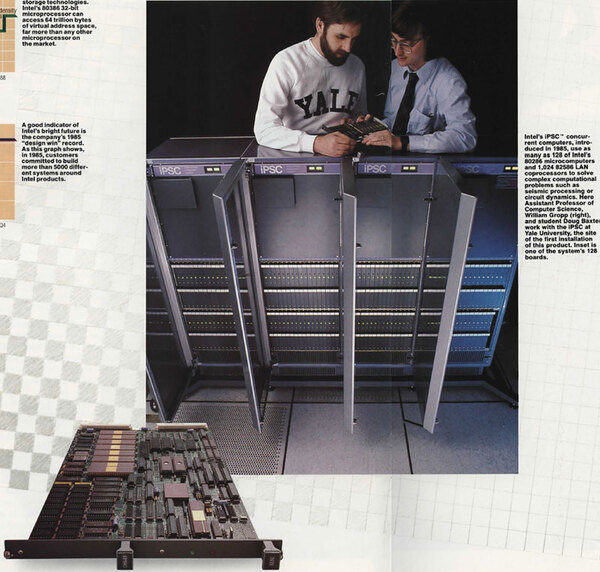

このSCGは、1985年に最初の製品としてiPSC(iPSC/1)と呼ばれるシステムを完成させる。iPSC/1はIntel System 310APと呼ばれるマイコンシステムをベースとしたものである。

PSCは“Personal SuperComputer”の略だ。上の画像にもあるように、この310APそのものは8MHzの80286をベースとした産業用PCに近い構成のものである。

この310APを最大4台組み合わせたものがSystem 310 APEXと紹介されているが、どうもこれをさらに拡張したものがiPSC/1になるようだ。

基本構成は310APに近いが、内部のボードを拡張して、ここに80287と512KBのメモリー、さらに最大8ポート分のイーサネットコントローラーをワンボードに搭載したものが1つのノードとなる。

このノードをキャビネットに32台集積したのが、最小構成のiPSC/d5で、2キャビネット/64ノードのiPSC/d6と4キャビネット/128ノードのiPSC/d7があった。また後追いの形で、ノード数を16に減らしたiPSC/d4もあったらしい。

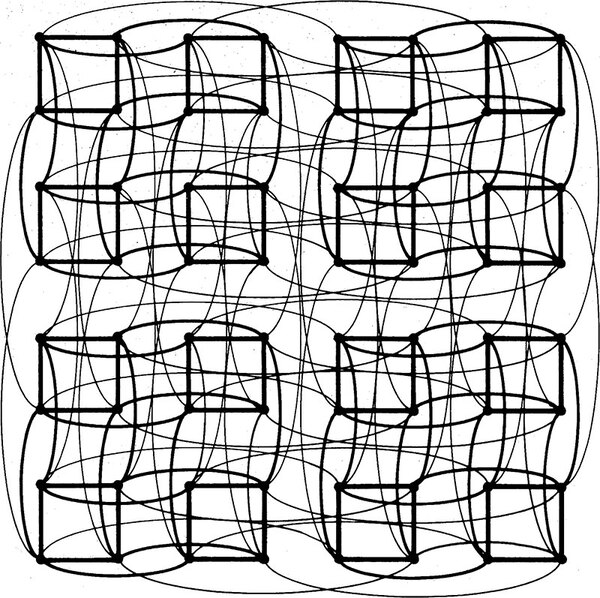

もともとこのシステムはCaltech(カリフォルニア工科大学)が1981年頃から研究していたCosmic Cube(PDF)が元になっている。

Cosmic Cubeそのものは64ノードの8086+8087のシステムを下の画像のような6次元のリンクで相互接続したシステムであるが、この各ノードの性能を引き上げるとともに最大128ノードに拡張したのがiPSC/1ということになる。

ちなみにノード間接続はイーサネットとされるが、当時のことだからまだ100BASE-TXはおろか10BASE-Tすらない時代なので、おそらく10BASE2を利用した接続であろうと考えられる。

基本的にはノード同士の直結なので、ほぼ理論値に近い速度で通信できただろう。128ノードの場合は7本のリンクでノード同士が接続される(1本はノードコントローラーに接続される、システム管理用リンク)ため、この7本のリンクが全部フルに転送を行なったら70Mbpsとなる。

これは当時のISAバスの実効帯域をややオーバーするほどなので、イーサネットであってもこれがボトルネックにはならず、先にノード内のISAがボトルネックになるはずである。

さて、このiPSC/1であるが、32ノード構成のiPSC/d5が1号機としてORNL(オークリッジ国立研究所)に納入されたことは間違いなさそうだが、性能などの評価に関する論文は見当たらない。ピーク性能は32ノード(1キャビネット)あたり2MFLOPSとされる。

搭載されてる80287の場合、まだパイプライン化されていないこともあり、例えばFADD(浮動小数点の加算)に70~100サイクルかかるため、一番高速な70cサイクルとして8MHz駆動だと0.11MFLOPS相当。これを32個集積しているから、ピーク性能は約3.7MFLOPSという計算もできるが、そこまで性能は上がらなかったようだ。

ORNL以外の販売先も不明であるが、何台かは販売できたらしい。ただ100台には達しなかったようだが、この性能では無理ないところだろう。

→次のページヘ続く (後継機のiPSC/2とiPSC/860)

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ