今回解説するのは、CRAY-1から枝分かれしたCRAY X-MPである。連載276回で説明した通り、CRAY-1の設計が一段落した時点でシーモア・クレイ(Seymour Cray)の関心はCRAY-2に移っていた。

CRAY X-MP

ただしCRAY-2の開発には延べ9年を要しており、それまでの間CRAY-1やCRAY-1Sなどで顧客を満足させられるかというと、これは非常に難しかった。というのはクレイの古巣であるCDC(Control Data Corporation)を筆頭とする競合メーカーが追い上げをかけていたからである。

そのためCRAY-2が出るまでの中継ぎが必要であった。その中継ぎとして、「CRAY-1のデュアルプロセッサー構成を作る」というアイディアを1979年頃に発案したのは、レス・デイビス(Les Davis)だといわれている。

レス・デイビスも元々はERA(Engineering Research Association)に属していたエンジニアであり、CDCを経てCRI(Cray Research, Inc.)に来ている。THE CHIPPEWA HERALDが2008年に行なったインタビュー(関連リンク)、あるいはコンピュータ歴史博物館による2010年のインタビュー(関連リンク)で、経緯が詳しく語られているが、最終的にデイビスはクレイの片腕とも言うべき立場になり、CRAY-1の開発を引っ張ることになった。

クレイとデイビスの関係については、国立アメリカ歴史博物館が収録している、1994年のMCI Information Technology Leadership Award for Innovationのインタビューがわかりやすい。テープ起こしした文章がこちらにあるが、デイビスについては、クレイ本人が「私は当時(CRIで)有能なチームを持ち合わせていなかったが、私を支援するという役割に関して彼の貢献は非常に大きく、ひょっとすると私より(CRIへの)貢献度は高いかもしれない。それは現在もそうだ」とベタ褒めしていることからも想像がつく。

クレイ自身は確かに天才かもしれないが、天才にありがちな現実処理能力の欠如や、他のメンバーとのコミュニケーションが下手といった欠点を持ち合わせており、こうした部分を補ったのがデイビスだったようだ。

ちなみにデイビスの次のスティーブ・チェン(Steve Chen)については「知らない、会ったことない、一緒に仕事したこともない」と、もう取り付く島もないほど冷淡なコメントが並んでいるあたり、実に対照的である。

話を戻すと、デイビスはCRAY X-MPの基本コンセプトを思いつくと、当時CRIのCEOだったジョン・ロールワーゲン(John Rollwagen)の許可を得て少人数のチームを形成して、実際に開発を始める。

したがってCRAY X-MPの開発主導権はデイビスが握っていたが、設計者としては主任デザイナーだったスティーブ・チェンが前面に出る格好になった。これはデイビスがあまり目立つのが好きではなかったから、ということらしい。

CRAY-1とさほど変わらない

CRAY X-MPの内部構造

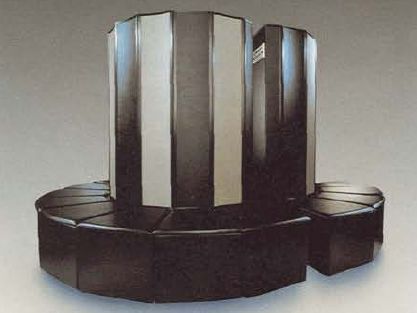

CRAY X-MPは、基本的にマルチプロセッサー構成のCRAY-1であり、プロセッサー数と搭載メモリー量に応じて11のモデルが当時のカタログに記載されている。

| CRAY X-MPのラインナップ | ||

|---|---|---|

| モデル名称 | プロセッサー数 | メモリー量 |

| X-MP/11 | 1 | 1MWords(8MB) |

| X-MP/12 | 1 | 2MWords(16MB) |

| X-MP/14 | 1 | 4MWords(32MB) |

| X-MP/18 | 1 | 8MWords(64MB) |

| X-MP/22 | 2 | 2MWords(16MB) |

| X-MP/24 | 2 | 4MWords(32MB) |

| X-MP/28 | 2 | 8MWords(64MB) |

| X-MP/216 | 2 | 16MWords(128MB) |

| X-MP/44 | 4 | 4MWords(32MB) |

| X-MP/48 | 4 | 8MWords(64MB) |

| X-MP/416 | 4 | 16MWords(128MB) |

“/”の後にある最初の数字がプロセッサー数、続く数字がメモリー搭載量(MWords)だ。もっともX-MP/1シリーズは、少しだけ高速なCRAY-1に過ぎないため、実際にはX-MP/2やX-MP/4シリーズが販売の中心になったようだ。ちなみに1982年に発表された当初のX-MPは2プロセッサーモデルのみで、1/4プロセッサーの構成は1984年に追加投入されている。

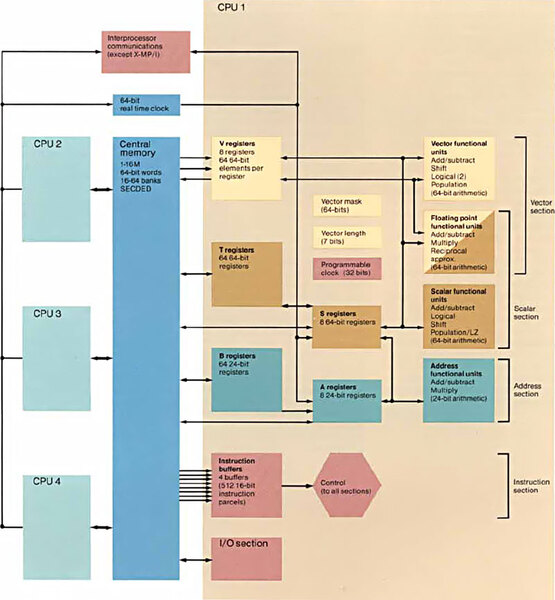

そのCRAY X-MPの内部構造だが、下の画像がX-MP/4の構成である。基本的にはCentral Memoryをすべてのプロセッサーで共有するのが大きな相違点で、さらにInterprocessor Communicationと呼ばれるユニットが新規に追加されている程度だ。プロセッサーの内部構造にはほとんど違いがない。

CRAY X-MPはCRAY-1とのソフトウェア互換性を最大限に保つように設計されており、実際オブジェクトレベルでCRAY-1とCRAY-X/MPには互換性が保たれていた。

回路そのものはECLベースで製造されたが、サイクル時間は9.5ナノ秒(105MHz)と、CRAY-1の12.5ナノ秒(80MHz)から30%程度短縮されており、これによりCPU単体でのピーク性能は210MFLOPSに向上した。またChainingに関しても若干の改良が施されたそうだが、こちらは調べたものの詳細は不明である。

相対的に大きな変更があったのはCommom Memoryの方である。CRAY-1とは異なり、最大4つのCPUから同時にアクセスが集中することになる。

この際に性能を落とさないようにするため、メモリーセルの構造はCRAY-1の2ポート(リード×1、ライト×1)から3ポート(リード×2、ライト×1)に変更されるなど、高速化というよりもマルチプロセッサー化で性能を落とさないための工夫が施された。

ただ設計開始からわずか3年での新製品投入だけに、そうあちこちを変更する余地はなかったというか、基本的にはマルチプロセッサー化とマイナーアップデートに留まっている。

むしろ大きな変更があったのはソフトウェアの方で、特にOSはマルチプロセッサーに対応させる作業が必要となった。当初は独自のCOS(Cray Operating System)が用意されたが、後追いでUNIX System VベースのCX-OSが、最終的にUniCOSという名称でリリースされる。このUniCOSは当初はゲストOSの扱いだったが、その後の改良により最終的にはメインOSになった。

→次のページヘ続く (SSDを採用、大ヒットとなったCRAY X-MP)

この連載の記事

-

第781回

PC

Lunar LakeのGPU動作周波数はおよそ1.65GHz インテル CPUロードマップ -

第780回

PC

Lunar Lakeに搭載される正体不明のメモリーサイドキャッシュ インテル CPUロードマップ -

第779回

PC

Lunar LakeではEコアの「Skymont」でもAI処理を実行するようになった インテル CPUロードマップ -

第778回

PC

Lunar LakeではPコアのハイパースレッディングを廃止 インテル CPUロードマップ -

第777回

PC

Lunar Lakeはウェハー1枚からMeteor Lakeの半分しか取れない インテル CPUロードマップ -

第776回

PC

COMPUTEXで判明したZen 5以降のプロセッサー戦略 AMD CPU/GPUロードマップ -

第775回

PC

安定した転送速度を確保できたSCSI 消え去ったI/F史 -

第774回

PC

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今 -

第773回

PC

Sound Blasterが普及に大きく貢献したGame Port 消え去ったI/F史 -

第772回

PC

スーパーコンピューターの系譜 本格稼働で大きく性能を伸ばしたAuroraだが世界一には届かなかった -

第771回

PC

277もの特許を使用して標準化した高速シリアルバスIEEE 1394 消え去ったI/F史 - この連載の一覧へ