高速化に必要なガリウム砒素の採用を断念

代わりに立体積層で信号遅延を解決

さて、問題は10倍以上の高速化をどうやって実現したかである。開発当初、クレイはECLをベースとしたICでは、こうした高速回路は実現できないと見込んでおり、Rockwell Semiconductorと共同でガリウム砒素(GaAs)の利用を真剣に考えていた。

やや時代が前後するが、IEEEの主催したSuperComputing 88というスーパーコンピューターの学会イベントでクレイが行なった“Whats all this about Gallium Arsenide?”という講演の動画がYouTubeで公開されている。

1時間10分の長いものなので気軽に見られるものではないが、クレイがガリウム砒素を真剣に将来の半導体素子と信じていたことがよく伝わってくる講演である。

クレイは続くCRAY-3でガリウム砒素を利用したシステムを作り上げたが、CRAY-2の開発には時期尚早であった。結局1980~1981年頃(この数字はあまり厳密ではない)に、ガリウム砒素の採用を断念、通常のECLベースの回路で製造するという方針を定めたようだ。

しかし、CRAY-1の世代ではCRAY-1SがECLベースで80MHzの性能を確保できたが、240MHzともなると3倍である。この際問題になるのは絶対的な動作周波数ではなく、配線遅延である。

最近のCPUと同じく、動作周波数そのものはパイプラインの細分化など色々方法があるが、素子と素子の間の配線遅延が大きくなると、それも限界がある。

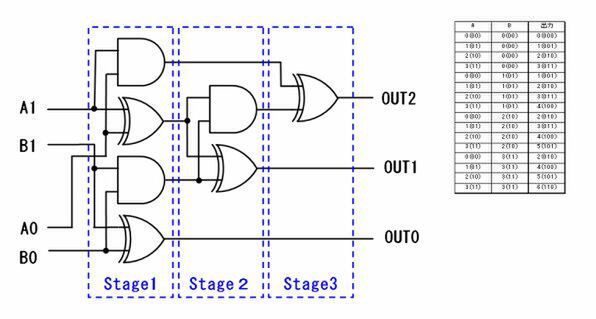

昔の記事に戻るが、連載237回の中で図3として示した2bitの加算器は3つのステージで動作する。

もしも回路が非常に大規模で、Stage 1~3が1枚の基板に収まらない場合、それぞれを別の基板にしたうえで、Stage 1とStage 2、Stage 2とStage 3をバックプレーンでつなぐことになる。

ところがこのバックプレーン経由での接続は、しばしば各々のステージと同じ程度の所要時間となる。配線遅延がどの程度か、というのは材質(正確には比誘電率εr)で変わってくるが、大雑把にはεrが1に近いというかなり理想的な状態でも100ps/inch程度だ。

つまり2.54cmを移動するのに100ps(0.1ナノ秒)かかる。ということは配線長が25.4cmなら1ナノ秒。1mほどの配線になると4ナノ秒となり、CRAY-2の設計サイクル時間に等しくなってしまう。

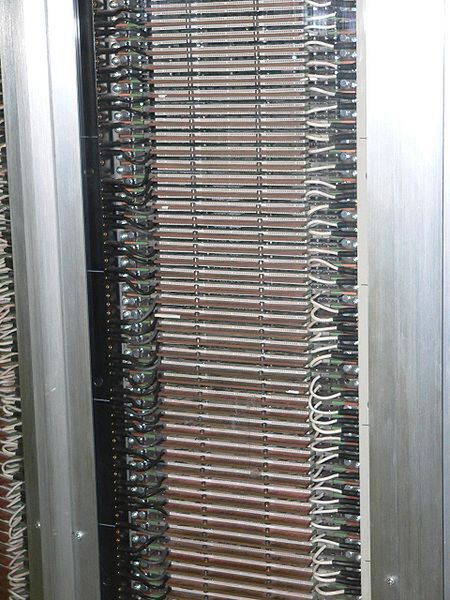

「配線が1mもあるか?」と思われるかもしれないが、前回の内部構造を見ていただくとわかるが、カードが結構大きいうえ、シャーシも人間の背の高さほどある。

カード→シャーシ内のバックプレーン→カードという配線経路(と、カード上の配線経路)を考慮すると、1mまではいかないにしても0.5m位には簡単になってしまいそうである。実際は配線材料の誘電率がもっと大きいので、制限はさらにきつくなる。

こうなると、配線遅延を減らすためには「なるべく1枚のカード上に回路を多く乗せることで、配線の物理的距離を減らす」のが得策である。

ところが当時のICでは物理的なサイズが大きいうえに表面実装やBGAなどの小型パッケージはないし、自動リフローマシンなどもないため、手作業での半田付けを行っており、この作業が困難極まりなかった。

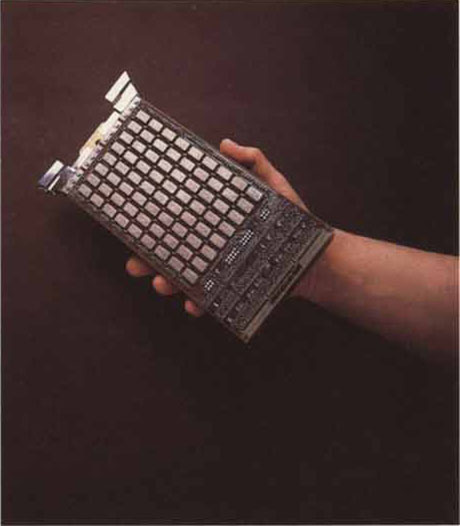

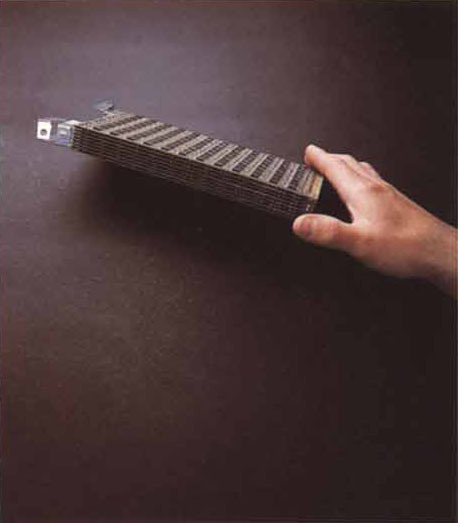

試行錯誤の結果、最終的にはボードの立体積層という形になる。これはICを搭載したボードを8枚積層し、間を垂直貫通の信号ピンでつなぐ方式である。

この塊をCRAY-2ではモジュールと呼ぶが、このモジュール内部の信号遅延は低めに抑えることが可能になり、結果として当初予定していた4.1ナノ秒というサイクル時間が実現できた。

→次のページヘ続く (モジュールは液体に浸して冷却)

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ