SiSチップセットの歴史 その2

ハイエンド路線には乗れず バリュー向けで終わったSiS

2010年05月31日 12時00分更新

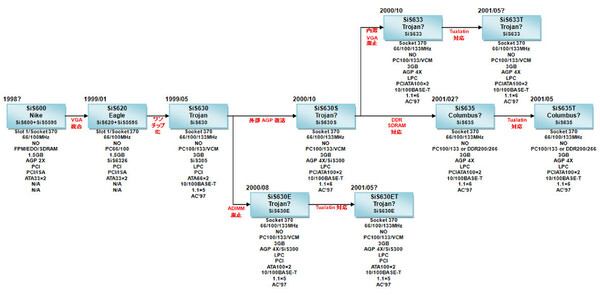

P6バス世代最初の製品は、Socket 7版を改良した「SiS600」

前回の最後で解説した「SiS500」シリーズのラインナップに続き、台湾SiSは1998年にインテルのPentium II/III向けのチップセットとして、「SiS600」シリーズを用意する。最初の製品はSiS600だが、これはSocket 7用の「SiS5591」を、Slot 1/Socket 370対応にしただけのものである。

さらに、実はこのSiS600、ややフライング気味に発売されたものである。というのは、インテルからのバスライセンス供与の契約が結ばれたのは1999年1月のことだ。ところが、その時点ですでにSiS600を搭載した製品が存在していたということは、少なくともOEMベンダーにはライセンス契約の締結前に出荷していたことになる。といっても、性能的には見るべきものはなく、採用するベンダーも数少なかった。

インテルとのライセンス契約が締結されたのに合わせて、今度は「SiS530」をSocket 370対応にしたとでも言うべき「SiS620」を、1999年1月にリリースする。これに続き、1999年5月に発表したのが「SiS630」であり、これは初のワンチップ化したチップセットである。

もっとも、パッケージはワンチップだったが、これはノースブリッジとサウスブリッジの2つのダイを、MCMで1パッケージに搭載したものだったようだ。外部AGPバスなどは持たない代わりに、AGPスロットをそのまま流用する(ただし配置は通常の逆)形で「ADIMM」なるローカルフレームバッファを利用できる構造になっていた。

しかし、このADIMMをきちんと利用するベンダーはほとんどなかった。そのため2000年には、廉価版としてADIMMのサポートを廃止した「SiS630E」をリリースする。またSiS630のAGPポートを復活させた製品を「SiS630S」として、これから内蔵GPUの「SiS300」を省いた製品を「SiS633」として、どちらも2000年10月にリリースする。

さらに、SiS630SにDDR-SDRAMのサポートを追加した製品を、「SiS635」として2001年2月にリリースする。このSiS630E/SiS633/SiS635については、その後Tualatin(0.13μmプロセスのPentium III)対応とした「SiS630ET」「SiS633T」「SiS635T」をそれぞれリリースし、このあたりでP6バス向け製品は終了する。

サウスブリッジ機能の問題で1チップ構成を諦める

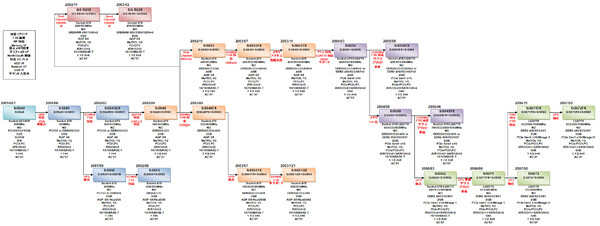

SiSはP6バスに続き、2001年3月にP4バスのライセンスも取得する。これを受けて、最初に投入された製品が「SiS640」であるが、これはSiS630Eあたりに非常に近いローエンド製品であった。

これに続き、1チップ構成から2チップ構成に変更して、GPU統合をやめた「SiS645」が、2001年8月に登場する。SiS645を2チップ構成とした理由について、「P4バスはQDR(Quad Data Rate)構成なので、データレートが上がるために発熱が増える。そのためワンチップでの実装が難しい」と、当時SiSは述べていた。ただしこれは建前だ。実際には主要なOEMベンダーすべてから、「1チップ構成をやめるように」と強い要請があったためだ。

1チップの何が問題だったかというと、この頃のSiSのサウスブリッジ機能には、控えめに言っても「問題があった」からだ。有名なところでは、USBコントローラーにかなり深刻なバグがあり、特にSiS630/630Eの2チャンネル/5ポートという不思議な構成のUSBコントローラーや、その後継であるSiS633/635の2チャンネル/6ポートのコントローラーは、当初まともに動かないほどだった。

問題はないにこしたことはない。だが仮に問題があっても、2チップ構成であれば最悪でもサウスブリッジだけを取り替えれば対応できる。ところがMCMによる1チップ構成だと、チップセット全部を取替えになってしまい、対応が非常に難しい。こうしたこともあって、OEM筋から(トラブルがあった場合の対策を容易にするために)2チップ構成にすることを強く求められた、というのが本当のところである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ