1次命令キャッシュが32KB→64KBに増量

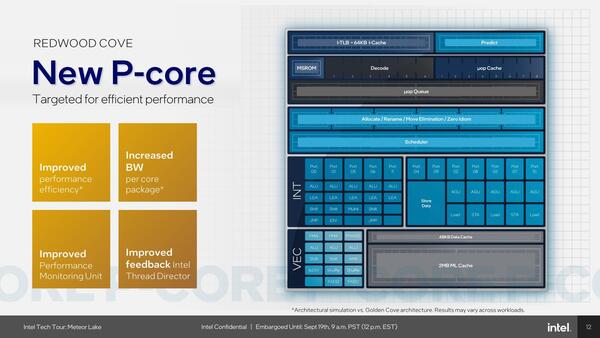

次は、そのMeteor Lakeを構成するPコアのRedwood CoveとEコアのCrestmontである。まずRedwood Coveの構造が下の画像だ。

連載736回でも書いたが、Redwood CoveはGranite RapidsとMeteor Lakeの両方で採用されるわけだが、そのGranite Rapidsのブロック図と比較すると、予想通りマトリックス・エンジンはMeteor Lakeには搭載されないようだ。これは当然で、AVX512ですら有効化されているか怪しいのに、AMXを搭載するわけもない。

内部構造をAlder LakeのGolden Coveと比較した場合、異なっているのは1次命令キャッシュが32KB→64KBに増量されたこと、それとPort 10と11の役割が逆転していること程度である。

2次キャッシュが2MBというのはRaptor Lakeに搭載されたRaptor Coveですでに実現しているので、性能改善につながる目立った項目は1次命令キャッシュの容量しかない。

実際には細かい改良などが施されているだろうから、いくつかの命令でスループットが上がったりレイテンシーが下がったりといった違いはあるだろうが、基本的には従来と変わらず、あとは動作周波数次第という感じである。

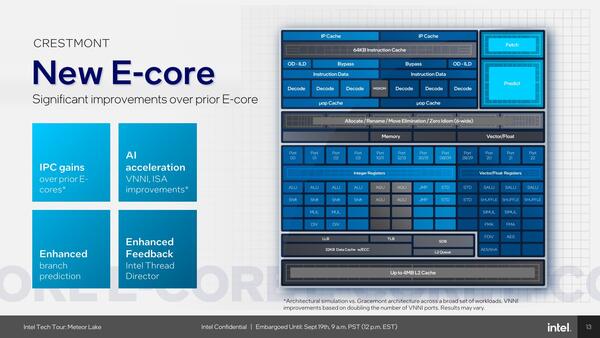

一方のEコア。ここで利用されているCrestmontはSierra Forestと共通である。違いがあるとすれば、コンシューマー向けであるからメモリーサブシステム周りはSierra Forestに搭載される“Xeon Advanced Features”はまるっと無効化されているものと思われる。

ただこれを除くと基本的にはまったく一緒であり、そうなるとSierra Forestのところで説明したように基本的なIPCにはほとんど差がないことになる。こうなると、このスライドに出てくる“IPC gains over prior E-cores(以前のEコアに比べて IPCが向上)”をどうやって獲得しているのかは現時点でははっきりしない。

少なくともVNNI周りの命令が多少高速化されたのはわかるし、分岐予測のメカニズムに改良があったらしいこともわかるのだが。

このあたりは12月の製品出荷に合わせて公開されるであろうSystem Optimization Manualあたりで出てくるかもしれない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ