ロードマップでわかる!当世プロセッサー事情 第701回

性能が8倍に向上したデータセンター向けAPU「Instinct MI300」 AMD CPUロードマップ

2023年01月09日 12時00分更新

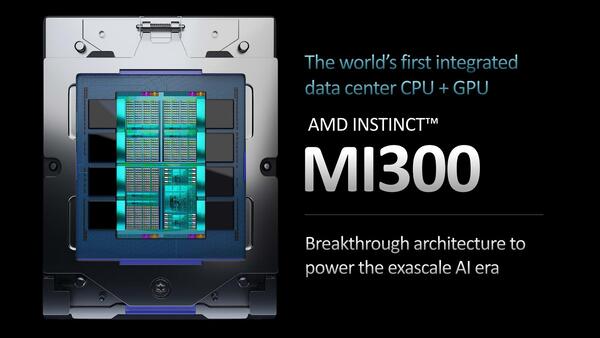

CES 2023におけるAMDのLisa Su CEOの基調講演の内容そのものはレポート記事にまとめられているので繰り返さないとして、今回は最後に紹介された隠し玉であるAMD Instinct MI300の話をしたい。

Instinct MI300に関しては情報が少ないのだが、2022年6月のFinancial Analyst Dayである程度まとまった話が出てきた。この時に出てきた情報は連載672回でまとめて説明したのだが、ただ筆者としてもいろいろ読み違いしていることが今回はっきりわかったので、その訂正も含めて新しい情報をまとめてみたい。

CPUとGPUとHBM3を1つにした

Instinct MI300

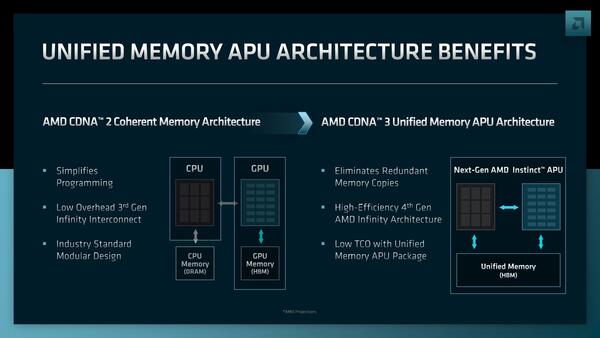

昨年、上の画像が出ていた時点で気が付くべきだったのだろうが、Instinct MI300は本当にCPUダイとGPUダイ、さらにHBM3メモリーまでを1つのパッケージに収めたAPUの構造になっていた。

連載672回での説明は、CPUは別パッケージになって、MI300とCXLで接続することを前提にしたものであるが、これが根底から崩れたことになる。

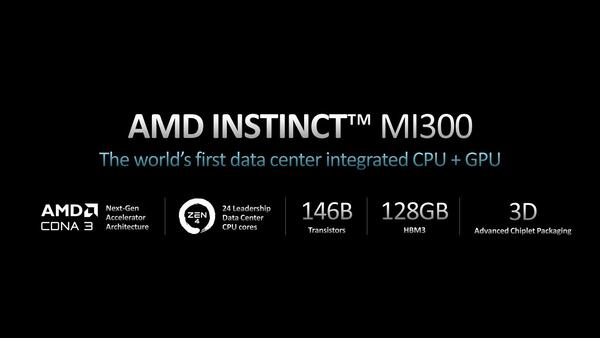

さて、基調講演でのSu CEOの説明では、このInstinct MI300は9つの5nmチップレットと4つの6nmチップレットを、3D積層で接続したとしている。総トランジスタは1460億個で「AMDがこれまで製造した製品の中で最も複雑」というのもよくわかる。

メモリーはHBM3が128GB。8層なので1層あたり16GBとなる。スピードは不明だが、定格(6.4Gbps/pin、1024pin)だとすると1層あたり819.2GB/秒。これが8層では6.56TB/秒に達する計算だ

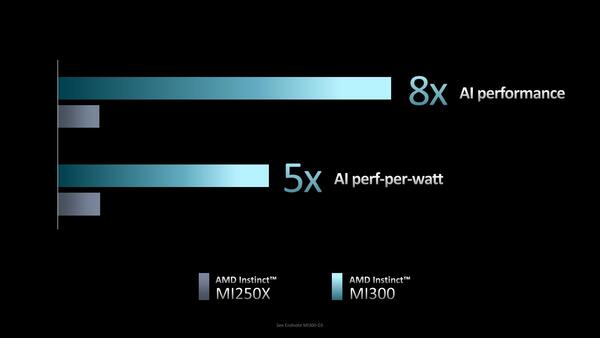

ちなみに同じようにマルチチップレットを3D積層を用いて製造したインテルのPonte Vecchioの場合、総トランジスタ数が1000億個以上とされている。正確な数字はわからないのでどちらが上とは言えないが、ほぼ同クラスの複雑さを持っていることがわかる。性能/消費電力比そのものは以前も示された数字だが、性能8倍は今回初公開である。

性能8倍は今回初公開。性能/消費電力比は5倍は連載672回でも示されている

このAMD Instinct MI300は、2023年後半に投入予定とされる、というのが基調講演における説明である。

最初のターゲットの1つが、ローレンス・リバモア国立研究所のEl Capitanだろう、という話は連載554回で説明した

この連載の記事

-

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 - この連載の一覧へ