ロードマップでわかる!当世プロセッサー事情 第598回

最後のAtomとなるChromebook向けプロセッサーのJasper Lake インテル CPUロードマップ

2021年01月18日 12時00分更新

Rocket Lake-Sのダイサイズは8コアで219mm2

インテルCPUとしてはかなり大きい

さて、そのRocket Lake-Sの特徴そのものは従来から発表されているものと大して変わらない。ただ今回ダイショットが公開されたので、これをベースに分析してみた。

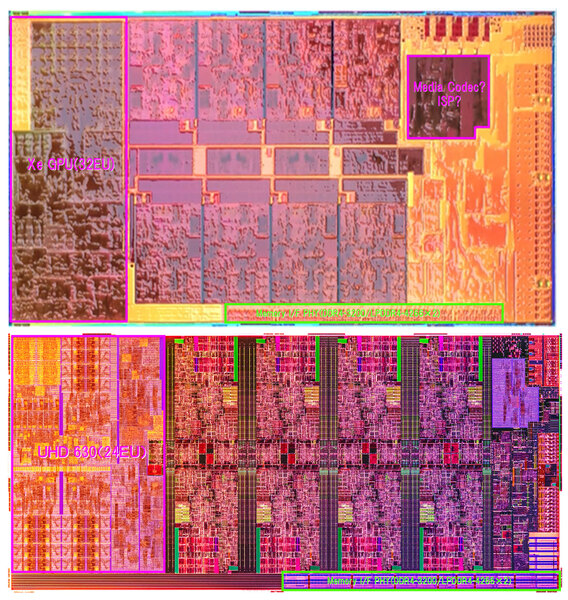

下の画像は上が先の画像から切り抜いて歪みを修正したうえで縦横比を調整したRocket Lakeのもの。下は8コアのCoffee Lakeのダイショット(以前インテルが提供したもの)である。

ここで縦横比の調整だが、どちらも14nmプロセスで製造しているので、DDR4/LPDDR4のI/F部のPHY(最下層の物理層)の寸法は同じであろうという仮定のもとに、このPHY部分(緑色で囲った部分)が同じサイズになるように調整した形だ。

8コアCoffee Lakeのダイサイズが180mm2前後とされていることから考えると、8コアRocket Lakeのダイサイズはおよそ219mm2と算出される。横幅はわずかに短いが、縦方向が1.2倍ほどに伸びている。これはおそらく個々のCPUコア(+3次キャシュ)の高さが2割ほど伸びて、これがそのまま反映されている格好と思われる。

不思議なのはGPUである。桃色で囲った部分がGPUになるが、Coffee LakeのIntel UHD 630(24EU)がおよそ45.4mm2、対するRocket Lakeはおよそ45.9mm2と算出された。それもあって、ひょっとしてRocket LakeのMedia Processing Engineは右側のブロックに移動したのではないか? と図には記しておいた。

ただCoffee Lakeの方も良く見ると横が3列に分かれており、EUが実装されているのは左の2列だけ(しかも一番左上にはEUが配されていないように見える)。残りのブロックはGPUのBack EndやMedia Encode Engineその他がごちゃごちゃ詰まっている感じであり、Rocket Lakeはこうしたもののかなりの部分を右側のUncore部に移動させたのではないか? という気もする。そうであれば、桃色で囲った部分がほぼ同じ面積でもそれほど不思議ではない。

それはともかくとして、8コアで220mm2近いというのは、インテルとしてはかなりのビッグサイズのダイである。なにせ10コアのComet Lakeが200mm2そこそこなので、Comet Lakeの12コア構成相当のダイサイズになる。確かにこれは10コア製品が出ないわけだ。

そしてこれだけダイサイズが大きければ、ピークの消費電力が増えるのも仕方ないところだろう。連載596回でも書いたが、Rocket LakeはK付きがTDP/PL1 125W、PL2が250W。KなしがTDP/PL1 65W、PL2 224Wだそうであるが、K付きにしてもKなしにしても、実際はPL1の枠で動くことは少なく、すぐにPL2まで上がる振る舞いをしそうで、実際のアプリケーション利用の際の平均的な消費電力がどのくらいになるかはきちんと確認しておく必要がありそうだ(測定が面倒そうだが)。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ