Xe LPコアの動作周波数を抑えたのはバランスを考慮したから

これ以上動作周波数を上げても性能的に寄与は少ない

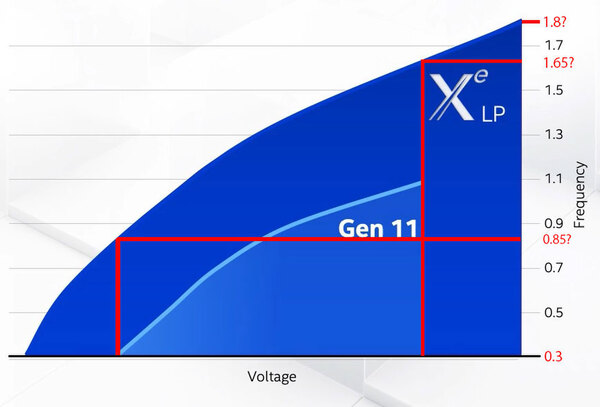

次に連載577回で少し触れた、GPU動作周波数について。

上の画像で説明したように、Tiger Lakeに搭載されるXe LPコアは、Gen 11と同じPower Envelopeで最大1.65GHzまで引き上げ可能とみられる。にもかかわらず、例えばCore i7-1185G7の場合は最大でも1.35GHzに抑えられている。

その理由を尋ねたところ、「確かにPower Envelopeで言えばその通りだが、別のSKU、例えばDG1は(1.35GHzより)もっと上まで伸びる。4コアのTiger Lakeではバランスを考えて1.35GHzにした」という返事であった。

実は1.35GHzでもすでにメモリ帯域的にはオーバーしている。連載579回で説明したように、XeのEUは1サイクルあたりFP32/Int32で16Ops処理ができるので、64Bytes/サイクルを扱える計算になる。

Tiger Lakeでは96EUなので、1サイクルあたり6144Bytes、これが1.35GHzで動くとなると、ピークで8294.4GB/秒をGPUで取り扱える計算になる。

もちろん実際にはキャッシュもあるし、そもそもこんな風にひたすらデータを書き出すだけの処理が続くことは想定していないので、実際に必要な帯域はもっと低くなるのだが、ゲームなどで利用される帯域を考えると、これ以上動作周波数を上げても性能的に寄与は少ないと判断されたのだろう。

逆にDG1はTiger Lakeと比べてメモリー的にゆとりがある。Tiger Lakeと異なりCPUコアが存在しないので、メモリーバスの帯域を100%、GPUに充てられるからだ。 そのため、もう少し動作周波数が引き上げられると思われる。

4コアと2コア製品に続き

Tiger Lakeの8コア製品も投入される

現在のTiger Lakeは、4コア製品とCore i3向けの2コア(これは4コアのダイを流用)製品のみであるが、今後Tiger Lakeベースの8コア製品も投入されることがPhelp氏の発言により確認された。

したがって、Tiger LakeはGen 10で2つに分離してしまった製品ライン(4コアまでのIce Lakeと、6コア以上のComet Lake)の両方の後継製品となるわけだ。

Phelp氏は投入時期などは一切語らなかったが、普通に考えれば来年以降ではないかと思われる。おそらく6コア以上は現在のH-SKUに投入されることになるので、先のOperation Rangeで言えば35~45Wあたりを狙う製品となると思われる。

Alder LakeはLakefieldの後継アーキテクチャー

デスクトップとモバイルの両方の市場がターゲット

最後に今後の話を少しだけしよう。Alder Lakeの位置づけである。「Raja氏がArchitecture DayでAlder Lakeについて触れたが、これはTiger Lakeの後継となるのか?」と聞いたところ「Alder Lakeそのものはアーキテクチャーの名前で、これは強いて言えばLakefieldの後継となる。これはデスクトップとモバイルの両方の市場で、高性能と低消費電力を両立できる良いアーキテクチャーになる」としたうえで、「Tiger Lakeは製品のコード名だからAlder Lakeとは違う」という返事であった。

では2021年の製品はAlder Lakeベースになるのか? という質問に対しては、「将来製品の話はできない」という至極真っ当な返事であったが、そもそもAlder LakeがGolden CoveとGracemontの組み合わせになるわけで、Golden Coveをそのまま使った製品が出ても不思議ではない。

インテルはこのあたりと意図的にぼやかしており、どちらに進むのかははっきりしない。これはAMDへの牽制の意味もあるのだろう。それでも、とりあえずAlder Lakeがデスクトップにも使われることがインテルの担当者から明言されたことは、ちょっとした成果であった。

もっとも直近で言えば、2021年のデスクトップ向けはRocke Lakeベースで、Alder Lakeのデスクトップ版は2022年になるといった話が流れてきており、これだけ時間があるとまだ二転三転しそうな余地があるのはやや怖いところだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ