ロードマップでわかる!当世プロセッサー事情 第579回

Tiger Lakeの内蔵GPU「Xe LP」は前世代のほぼ2倍の性能/消費電力比を実現 インテル GPUロードマップ

2020年09月07日 12時00分更新

このロードマップ連載もすでに579回、第1回から数えると11年を超えて12年目に入るわけだが、その中でインテルのGPUというテーマで取り上げるのはこれが最初である。

もちろんLarrabeeなどは扱ったし、チップセットの絡みでG965の回で部分的に触れたりはしたが、(GPGPUではなく)GPUとして扱うのはこれが初めてだったりする。ということで、今回は少し昔の話から。

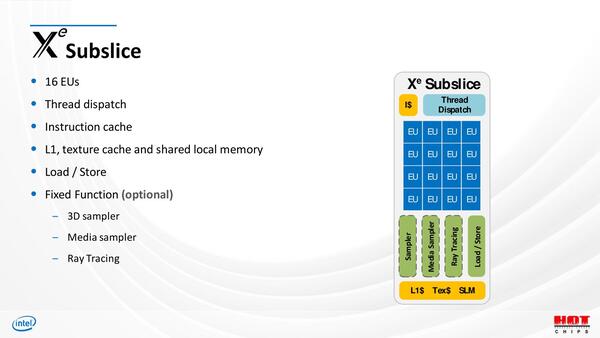

16のExecution Unitで構成される

XeのSubslice

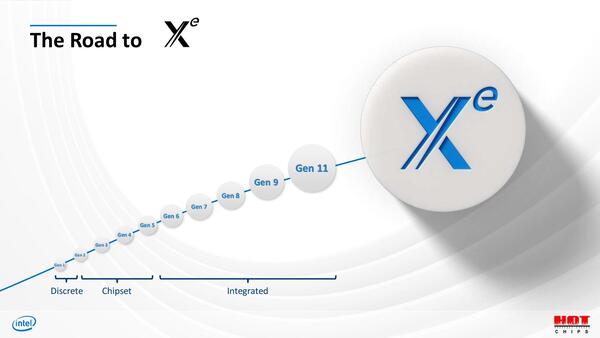

下の画像はXeに至る道ということで、Gen1(Intel 740のことだ)~Gen11を経てTiger Lake世代からXeに切り替わるという歴史を語っている。

Gen2は当初Intel 752/754として外付けで発売予定だったが、あまりにGen1(Intel 740)の評判が悪かったためにキャンセル。このグラフィックコアを流用したのがIntel 810やIntel 815である

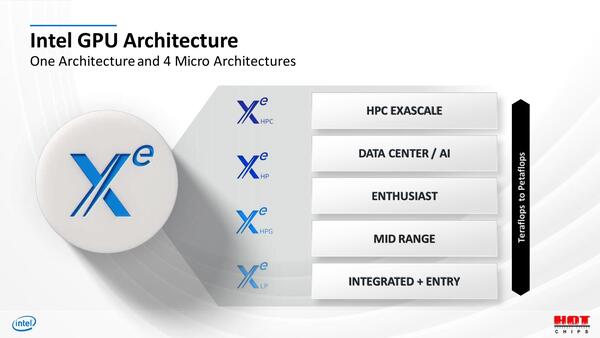

さてそのXeだが、以前はXe LP/HP/HPCの3種類しか存在しなかったのが、今回Xe HPGというエンスージアスト向けGPUがラインナップに加わったことが明らかにされた。

もっとも連載472回で紹介したどうみてもただのモックアップな画像を鑑みるに、エンスージアスト向けは最初から既定路線で、一時的にひっこめていただけかもしれない

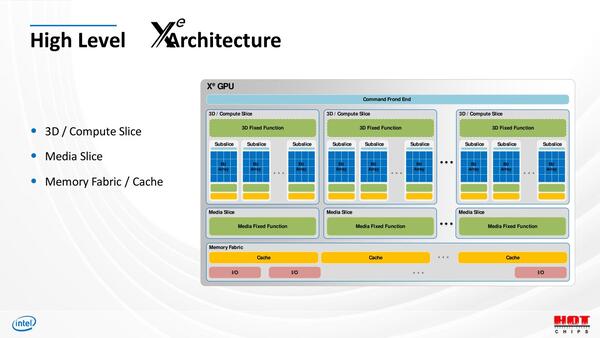

そのXeの基本構造がこちら。各々のユニットをどの程度内蔵するかはSKUによって当然変わってくる。

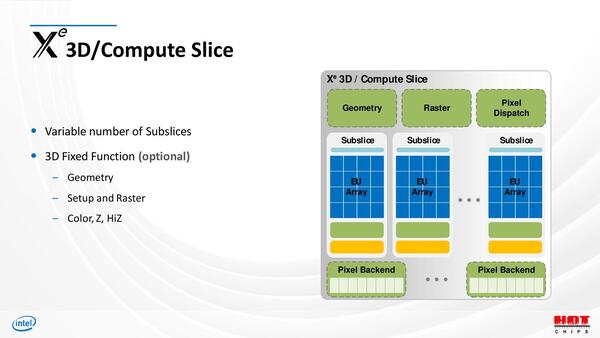

まず3D/Compute Sliceの構造がこちら。Subsliceの数も変更可能になっている。

おのおののSubsliceの構造がこちら。16EU(Execution Unit)とキャッシュ、Thread DispatchとLoad/Storeユニットは共通で、SamplerやRay Tracing Unitはオプション扱いである。

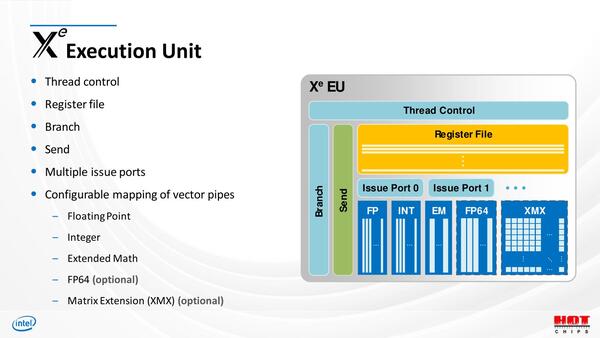

下の画像がEUの詳細だが、これだとややわかりにくいかもしれない。

EUの詳細。XMXは、おそらくであるが連載569回で紹介したAMXに対応するもの(CPU側がAMX、GPU側がXMX)と思われる。つまりXe GPUがCPUのアクセラレーターとしてシームレスに連携して動くと期待される

下の画像2つはArchitecture Dayの資料だが、Gen11までのEUは4-wideのFP/Int ALUと同じく4wideのFP/Extended Math ALUの組み合わせになっており、これを利用することで最大8wideの演算が可能であったが、ただしExtended Mathが発生すると右側のエンジンはそれに占有されてしまうので、4wide相当に性能が落ちることになる。

Gen11 EUの場合、1サイクルあたりFP32とInt32のMAC演算なら16FLOPS、FP16なら32FLOPSの演算だった。積和(=1演算が2FLOPS)での数字なので、要するに8本の演算パイプがフル稼働する形である

Gen11とのもう1つの違いは、Gen11はEUごとにThread Controlが独立しているが、Xeでは複数EUを横に貫く形でまとめてThread Controlが行なわれている。これで、スレッド制御がより効率的に行なえるとしている

対してXeでは、8wideのFP/INT ALU+2wideのExtended Math ALUという構成になり、Extended Mathと並行して8wideのALUが動作することになる。

したがってピーク性能そのもので言えばFP32やInt32が16FLOPS、FP16では32FLOPSということでGen11世代と違いはないが、実効性能はやや引き上げられた形になる。

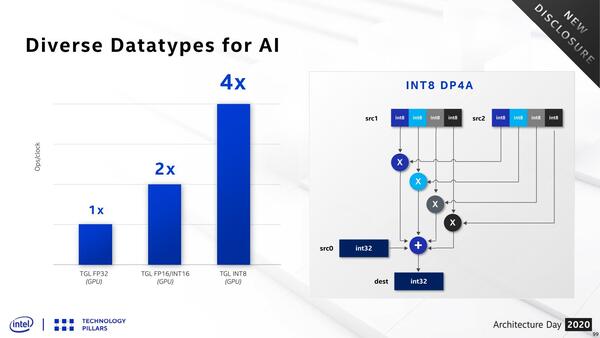

ちなみに、ここに出てくるDP4Aの処理は下の画像のようなもので、Dot Product(ドット積)の計算の際に利用される。Xe EUはこれを8wideで実行できるわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ