ロードマップでわかる!当世プロセッサー事情 第579回

Tiger Lakeの内蔵GPU「Xe LP」は前世代のほぼ2倍の性能/消費電力比を実現 インテル GPUロードマップ

2020年09月07日 12時00分更新

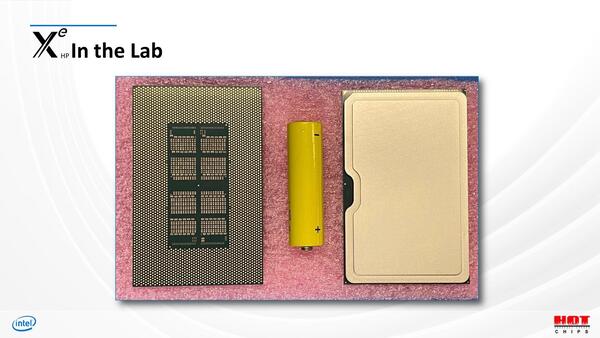

わりとパッケージサイズが大きい

Xe HP

Hot Chipsでは、これに加えてXe HPなどについてのプレビューも公開された。中央に置かれたバッテリーが単三電池相当だとすれば、パッケージサイズは52.8×81.3mmという結構大きなものになりそうだ。

Xe HPのダイが、ちょうど裏面のパスコンの真上に位置していると仮定すると、ダイサイズは23.4×22mmで514.8mm2という計算になる。GPGPU向けとしては手頃なサイズではないだろうか?

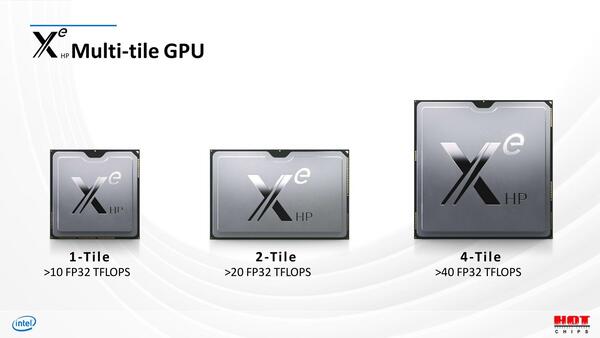

このXe HPは1/2/4Tile構成がある、という話は連載569回でも明かされていた。演算性能はFP32換算で1Tileあたり10TFlops、4Tileのもので40TFlopsとなる。

Int 8だとすると320Topsで、Raja氏のツイートに出てきた“(だいたい)1Pops”には遠い気がするのだが、どういう計算なのだろう?

このXe HPとXe HPCの(プロセス以外の)差が実はよくわからない。Xe HPにRAMBO Cacheなどを組み合わせたのがXe HPCというふうに筆者は理解しているのだが、間違っている可能性もある

TSMCの5nmは2021年末までに本当に間に合うのか?

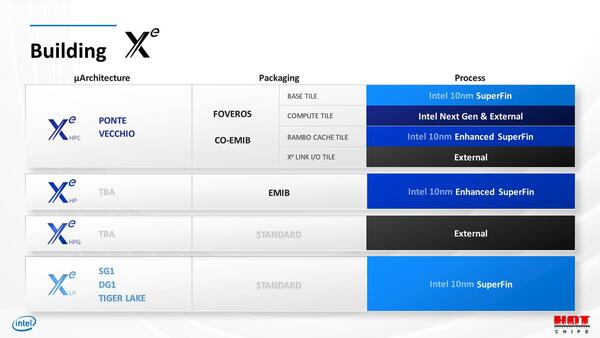

最後に製造プロセスだが、Xe LPは10nm SuperFinで、これはいい。そして連載569回に出てきたサンプルは10nm Enhanced SuperFinである。これは来年の投入であろう。

問題はPonte Vecchioで、Compute TileはIntel Next Gen & Externalというのは、要するにインテルの7nmかTSMCの5nmという話だ。Xe Link I/O TileはExternalだが、これはそれこそTSMCの6nmや7nmあたりだろう。

そしてRambo Cacheが10nm Enhanced SuperFinということで、そうなるとAuroraが予定通りに稼働しない公算が出てきた。連載435回で触れたが、Auroraは本来なら来年の今頃には設置が始まり、2022年末に検収完了となるはずだった。

ところがPonte Vecchioの要素の中でこれも確実に間に合うのはBase Tileと、Rambo Cacheがなんとかというあたりで、肝心のCompute TileがTSMCの5nmで本当に間に合うのか? という話である。

プロセスそのものはもうだいぶ安定してきたらしいが、はたして2021年末までにインテルの希望する数量の出荷ができるのか? はかなり不明確である。すでにインテルがTSMCの5nm向けCompute Tileをテープアウトしている、というのであれば可能だと思うが、テープアウトが来年だとかなり厳しいだろう。

またXe HPGは初めから外部Fab頼りになっており、それこそこれもTSMCの5~6nmあたりがターゲットではないかと思うが、こちらもどんなものになるのか、まだ見えてきていない。このあたり、今年中に何か動きがあるとおもしろいのだが。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ