ロードマップでわかる!当世プロセッサー事情 第569回

性能が70%向上するCooper Lakeと200Topsの性能を持つPonte Vecchio インテル CPUロードマップ

2020年06月29日 12時00分更新

毎秒200TBの処理性能を持つ

XeとPonte Vecchio

さてそのおじさんことRaja Koduri氏の話題。まず6月18日、Ryan Shrout氏(Chief Performance Strategist:前職はPC Perspective誌の編集)が、Xeを搭載したTiger Lakeのプロトタイプ上で、1080P/High Quality設定のBattlefield Vを動かしたデモの様子をTwitterに投稿した。

Perks of the job! Took a prototype Tiger Lake system for a spin on Battlefield V to stretch its legs. Impressive thin and light gaming perf with Xe graphics! Early drivers/sw, but it’s the first time I’ve seen this game run like this on integrated gfx. More later this year! pic.twitter.com/f1Qlz2jMyB

— Ryan Shrout (@ryanshrout) June 17, 2020

この動画、全画面表示にするとわかるが、FLAPSを併用しており(ということはDX11動作ということになる)、おおむね30fps以上を実現できていることが示された。

これがどの程度か、というのは評価が難しいが、かつて筆者がCore i9-9900K+GeForce GTX 1060で同じ条件(ただしDX12)でプレイした時がおおむね60fps強だったので、GeForce GTX 1060の半分程度のパフォーマンスが期待できる可能性がある。

もっともこれも、Ryzen 7 4800HSならさらに高速といった動画がカウンターで上がっていたりする(例えばこれ:https://www.youtube.com/watch?v=JuzDJMiSn_o)ので、正直製品が出てこないと評価は難しいのだが、少なくともIce Lake世代より格段に性能が上がったことは間違いなさそうである。

さて、連載511回でも書いた通り、7nm世代の最初の製品はXeベースのGPGPUになるという話が出ていた。このXeベースのGPUのコード名がPonte Vecchioと呼ばれているが、詳細は昨年11月に開催されたHPC Developer Conferenceである程度公開されている。

ここで公開された資料を全部紹介してるとあふれるので要点だけ述べると、XeそのものはSIMT+SIMDの構成で、しかもダイナミックに演算ユニットを変化させられるらしい。

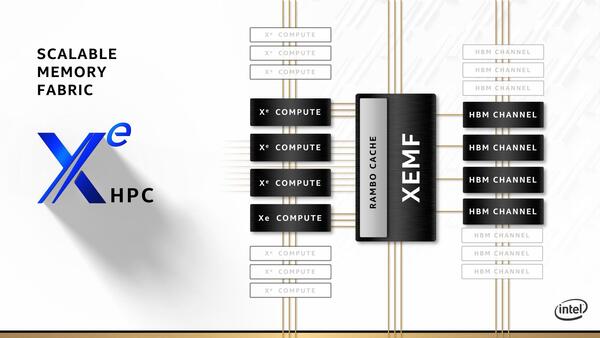

そして、このXeのCompute Unit×4にRAMBO CACHEと呼ばれるキャッシュ+メモリーコントローラーを搭載したチップを組み合わせて、1つのパッケージになるとされている。

ということでそのKoduri氏、6月25日に複数のメンションを投稿している。まずはこれ。Folsom(インテル本社そば)にあるXeのラボで、おそらくは実働テストの様子が示されている。

Miss the chaos and beauty of bringup labs..A day trip to Xe lab in Folsom pic.twitter.com/JKm90m5YB0

— Raja Koduri (@Rajaontheedge) June 25, 2020

1枚目の手前、赤いタグには“DG1x GPU A0 QU6T”とあり、そのわきには“DG1x GPU B0 QV2”とあるあたり、これはDG1ではなく、その後継製品(つまり7nmプロセスでの製品)と思われる。また2枚目は明らかに1枚目とは異なるチップで、パッケージからすると次のPonte Vecchioのテスト中に思える。

次のメンションがこちら。比較用の単三バッテリーからすると、左上のものが短辺48mmほど、長辺は70mmほどだろうか? 右上は48mm角、右下が70mm角程度に見える。先ほどの2枚目でヒートシンクの下にあったのは、右上の一番小さい奴に思える。

BFP - big ‘fabulous’ package?? pic.twitter.com/e0mwov1Ch1

— Raja Koduri (@Rajaontheedge) June 25, 2020

さてこれがなにか? だが、右上はXeの構成、右下がXe Compute×4(XMMFは別)の構成、左はXe Compute×2の構成に思える。

ここまでは良い。問題は次のメンションで、これは4つのXe Computeが収まったパッケージだが、これ1つで「おおむね1Pops」の処理性能を持つ、としていることだ。

And..they let me hold peta ops in my palm(almost:)! pic.twitter.com/8kG7cv774M

— Raja Koduri (@Rajaontheedge) June 25, 2020

“(almost:)”と書いてるあたり、実際には800Topsくらいな気がするが、だとすると1つのXe Computeで200Topsほどの処理性能ということになる。

サポートされる最小のデータ型はINT8なので、つまり毎秒200TBの処理性能を持つ、という計算になるのだが、どうやってこれを実現しているのか想像がつかない。なんというか、より謎が増えた感はある。

加えて言うと、もしこのチップ1つで本当に800Topsが実現できるなら(そしてBFLOAT16の演算性能がINT8の半分程度と仮定したら)、Auroraはこのチップ2500個で完成することになる。いくらなんでも、少なすぎないだろうか? それもあって筆者は「実はtera opsの間違いでは?」と疑っている。このあたり、続報が入り次第またお届けしたい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 - この連載の一覧へ