今週はAIプロセッサーの話はお休みいただき、Lakefieldを取り上げたい。Lakefieldに関してはジサトライッペイ氏による第一報がすでに上がっているのでご存じの方も多いかと思う。

この連載でも538回でLakefieldのSmall core側であるTremontの内部解説をしているが、今回は発表でわかったこととまだわからないことをまとめて紹介したい。

ダイサイズは82mm2?

通常インテルは製品をリリースするとそのダイ写真なりウェハーイメージなりを紹介してくれるのだが、現時点でLakefieldに関しては公式(News Roomページ)では未公開である。

ただ本国では電話会議の形でプレスブリーフィングがあったらしく、その際に追加でダイ写真が紹介されたというAndreas Schilling氏のツイートがある(同氏はhttps://www.hardwareluxx.de/のエディターの1人)。

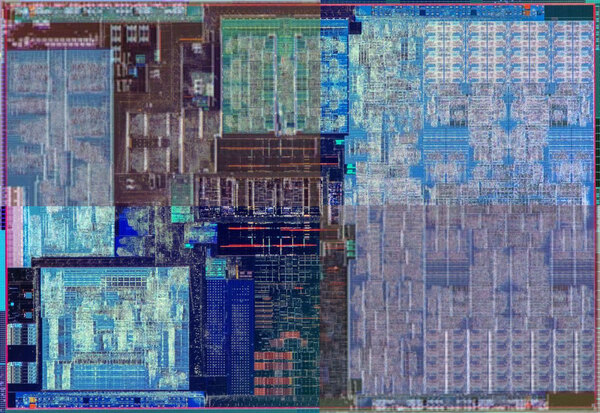

Better resolution die shot of the compute die of a #Lakefield processor. pic.twitter.com/U0wv4OjS9g

— Andreas Schilling (@aschilling) June 10, 2020

実はこれ、同じものを入手できないかインテルに掛け合っているのだが今のところ返事がない。なのでいまいち真偽のほどは不明ではある。ただ実は今年5月、imgurにLakefieldのダイ写真が上がっており、これのタイトルが“Intel LKF 82mm2”となっている。

この2枚を試しに重ねた結果が下の画像で、見事に一致しており、おそらくはどちらも正しくLakefieldのものと思われる。

一応このどちらもがLakefieldのダイ写真だと仮定した場合、ダイサイズは82mm2というimgurの数字がわりと信憑性をもつものになる。

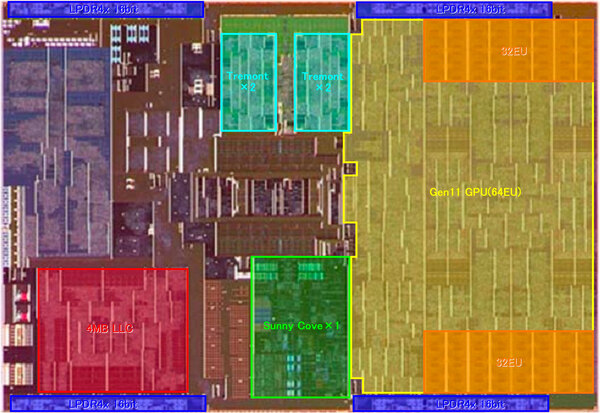

仮にこの82mm2が正しいとして内部解析をしてみたい。下の画像はimgurのイメージに、想定されるレイアウトを重ねたものである。

左上のブロックと左下ブロック、どちらがLLCかはかなり悩んだのだが、おそらくダイ左端中央にあるのがPCI ExpressのPHYで、となると左上はPCI ExpressのRoot Complexその他と考えられるため、左下がLLCと思われる

全体の4割近くをGen11 GPUが占め、中央にSunny Cove×1(下側)とTremont×4(上側)が並び、左側にUncoreの4MB LLCその他が集積される、わりと整然とした構成である。この画像からそれぞれのエリアサイズを推定すると、以下の表のようになる。

| Lakefieldのエリアサイズ | ||||||

|---|---|---|---|---|---|---|

| Sunny Cove | 4.8mm2 | |||||

| Tremont(1コア) | 0.93mm2 | |||||

Sunny Coveのエリアサイズは、Ice Lakeでは6.9mm2と伝えられているが、これはLLCのSliceを混みにした数字で、LLCなしでは4.7mm2程度とされるので、ほぼ今回の推定と一致することになる。

そしてここから今回Tremontコアのエリアサイズが初めてわかったわけだが、1つあたり1mm2未満、4コア合計でも3.7mm2ほどでしかない。

もっとも実際には2つのTremontコアのクラスターの間にインターコネクトが入っており、4コア全体でのエリアサイズで言えば5mm2をやや超えるほどになる。

とはいえ、4コアのTremontと1コアのSunny Coveがほぼ同等のエリアサイズになるわけだ。性能/エリアサイズ比では悪くない結果だと思う。

ちなみにLakefield自身は下の画像のように、Compute DieとBase DieをFoverosで結合し、さらにDRAMをPOP(Package on Package)の形で搭載する構造なので、別にBase Dieが必要になる。こちらのダイサイズは不明だが、おそらく同等もしくはやや大きい程度に抑えられていると思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ