CNN(畳み込みニューラルネットワーク)が実用になる、という話で2013年あたりから活発に業界がそちらに向けて動き始めたという話は過去3回でしてきたが、これに向けた専用プロセッサーの先鞭をつけたのはGoogleだった。

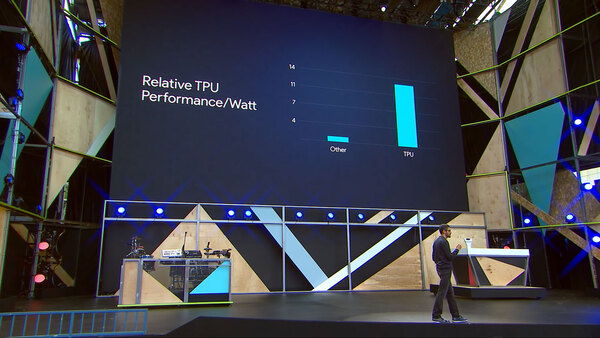

性能/消費電力比が競合と比べて10倍優秀

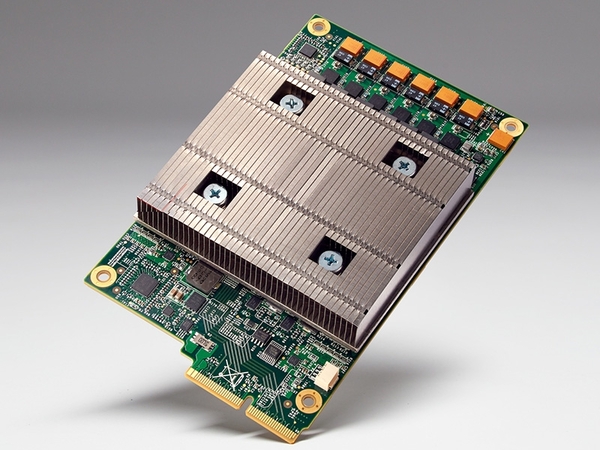

GoogleのAI向けプロセッサー「Google TPU」

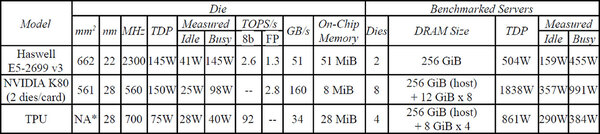

2016年5月に開催されたGoogle I/Oの基調講演で、GoogleはGoogle TPUを発表。絶対性能はともかくとして、性能/消費電力比が競合と比べて10倍優れていると説明した。

競合はおそらくNVIDIAのGPUだが、2016年5月はまだPascalが前月にリリースされたばかりなので、世代的にはMaxwellが競合となる。ただデータセンター向けのTeslaでは28nmプロセスのKeplerベースが最新であり、これとの比較とこの時点では思われた。

Google TPUもやはり同じ28nmプロセスで製造されており、アーキテクチャーを工夫することで10倍の効率を実現したというわけだ。

基調講演では、Google TPUがすでに稼働中であり、Google検索の要であるPageRankを評価するRankBrainやGoogle Street View、さらにはAlphaGoなどにも使われていることが明らかにされた。

そのGoogle TPUであるが、2017年6月に開催されたISCA(International Symposium on Computer Architecture)において“In-Datacenter Performance Analysis of a Tensor Processing Unit”という論文で詳細が明らかにされた。

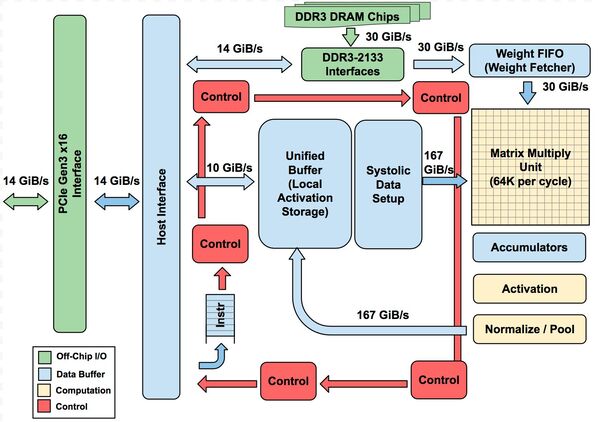

下の画像がその全体像である。計算部となるのは、256×256で65536個並んだMAC演算ユニットと、そのMAC演算の後処理で加算を行なうアキュムレーターである。もっともこれ、65536個のMACユニットが同時に演算できるわけではなく、言ってみれば256サイクルかけて出力されるようなイメージである(実際はもう少し早い)。

つまり256組の256 MAC演算ユニットがあるかたちだ。1サイクルあたりに出力される結果は1組分であり、パイプライン動作をしている格好だ。ただそれでも毎サイクルあたり256Bytesのデータ処理が行なわれるわけで、それに見合ったデータ転送性能が必要である。

例えば連載562回で例として掲載した図を例にとると、もともとの画像データはSystolic Data Setupと呼ばれるユニットから、フィルターのデータはWight FIFO(Weight Fetcher)と呼ばれるユニットから供給され、乗算→加算→活性化→プーリングを経てUnified Bufferに戻される。

このSystolic Data Setupと64KのMatrix Multiply Unit、およびNormalized/PoolとUnified Bufferの間は、256Bytes(=2048bit)幅のバスでつながっている。

要するに1サイクルあたり256Bytesの元データ読み込みが可能で、一方演算結果も同じく256Bytes/サイクルでUnified Bufferに書き戻せる構造になっている。ちなみにそのMAC Unitの下にあるアキュムレーターは、1サイクルで256個の演算結果の合計を計算可能になっている。

このTPUがどれだけスムーズに動作するかは、どれだけ切れ目なくデータをMACユニットに送り出し、かつ結果を受け取れるかにある。このため、Unified Bufferは24MB、アキュムレーターは4MBの容量を持っている。

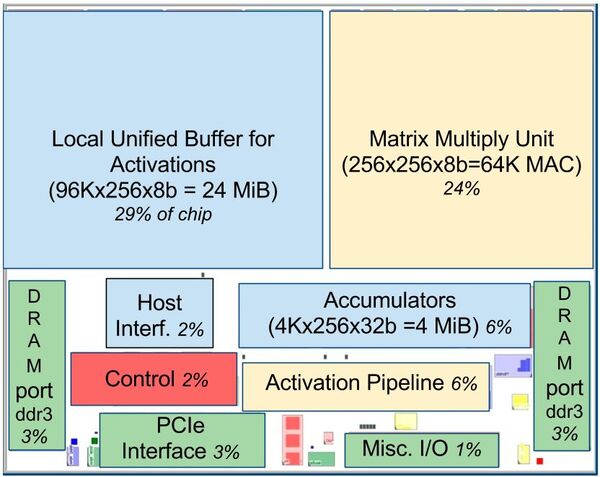

チップ内部のレイアウトは下の画像の通りで、バッファがかなり大きな容積を喰っているのがわかる。ただ24MBはキャッシュとしては十分であっても、システム全体のメモリーとしては不十分である。

これを支えるためにDDR3-2133×2chのメモリーが合計32GB搭載され、これで足りなければPCI Express経由でホストのメモリーを利用できるかたちだ。ちなみにヒートシンクの陰に隠れていた基板が下の画像だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ