配線のために生産ラインを再構成までした

MCM周り

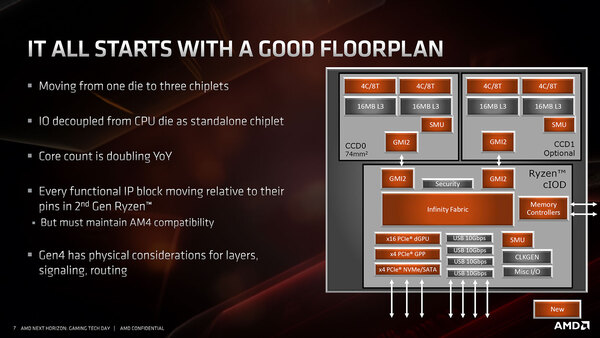

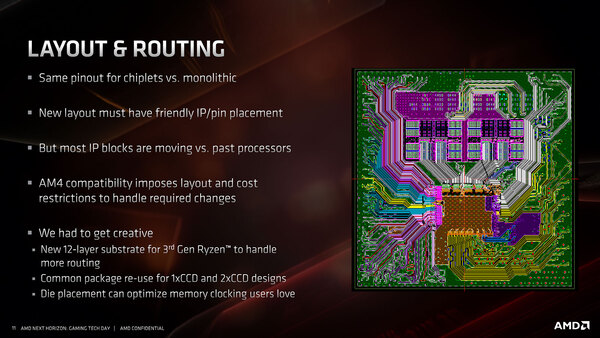

MCM周りについてもいくつか説明があったので紹介しよう。下の画像がRyzen 3000シリーズの内部構成である。

連載496回で、「インフィニティーファブリックのコントローラーがI/Oチップレット側に移動すると、Zen 2内部の制御(それこそSenseMIなどがインフィニティーファブリックの上で実装されている)が遅くならないか?」というのが、CCXを8コアでないかと考えた最大の理由だったのだが、こちらにその回答が入っている。

図中でSMU(System Management Unit)とあるのが、そのインフィニティーファブリックを利用したSenseMIを始めとするさまざまなシステム管理を司る部分である。つまり以下のことがわかる。

- CCXは引き続き4コアベース

- CCD(つまりCPUチップレット)全体の制御は、CCD内のSMUが行なう。同様にcIoD(つまりI/Oチップレット)の制御は、cIoD内のSMUが行なう

構図としては連載496回で図解したZenベースのダイの内部ブロックに近いものになると考えられる。

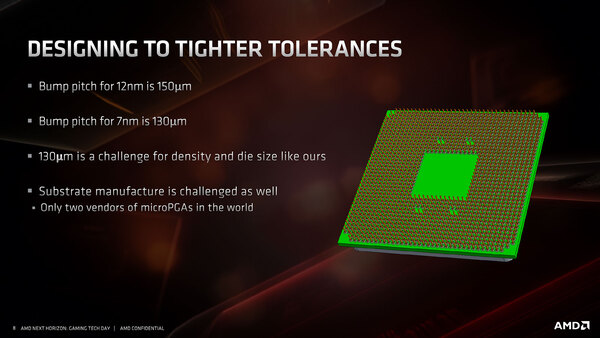

ちなみに一見すると簡単そうに見えるが、実際はI/Oチップレットが従来と同じ150μmピッチのボール状バンプ(メッキで形成した突起状の接続電極)なのに対し、7nmプロセスを使ったCPUチップレットではこれが130μmピッチに狭まったそうだ。

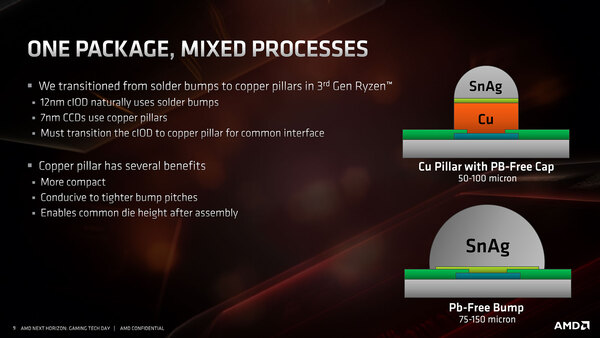

これを解決するために、従来のように配線に直接バンプを構成するのではなく、銅で柱を立て、その上にバンプを形成するという解決案を取ったそうである。

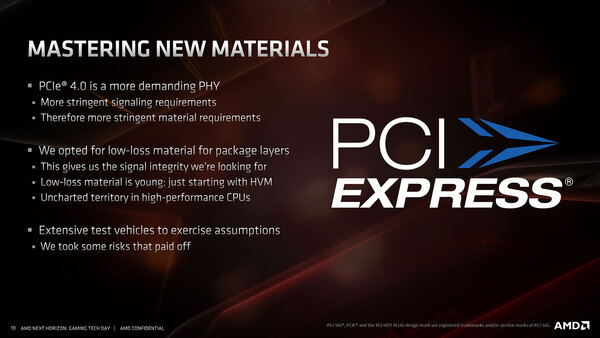

またこのRyzen 3000では既報の通りPCI Express Gen4をサポートするが、16GT/秒に達する信号速度に対応するために、パッケージの材質を改善して損失を減らす工夫が必要だったそうである。

下の画像がそのパッケージ層の配線で、おそらくは一番信号線のレイヤーだと思われるが、中央下のI/Oチップレットとその上に2つ並ぶCPUチップレットの間を直結しているのがインフィニティーファブリックの配線、左側に出ているのがおそらくはDDR4、そしてI/Oチップレットの中央および右上から、パッケージの右側に出ているのがPCI Express Gen4の配線と思われる。

実装もいろいろ大変だったそうで、生産ラインを再構成する必要があったというのも無理ないところである。

ということで、今回はCPU周りを深く掘り下げて解説した。全然性能やラインナップの話まで行けなかったのだが、このあたりはRadeon RX 5700シリーズ周りのまだ触れてない話題と併せて次週紹介する予定だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ