先週に引き続き、AMDのNext Horizon Gamingイベントで公開された話を解説しよう。今回はCPU編である。

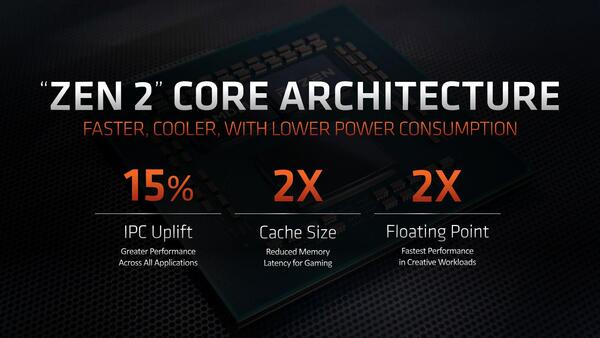

Zen 2ではIPCが15%改善

まずZen 2のコアアーキテクチャー全体で言えば、IPCが15%改善されているほか、3次キャッシュのサイズが2倍となり、またFPU性能も2倍になるとされる。

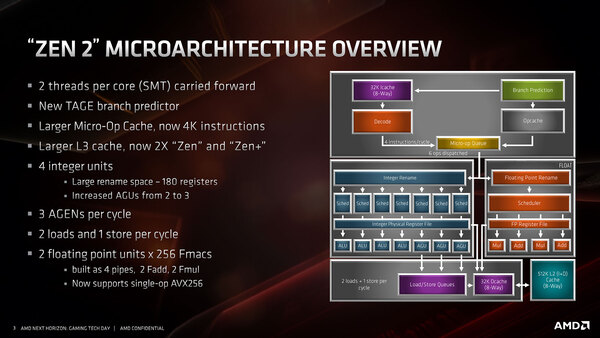

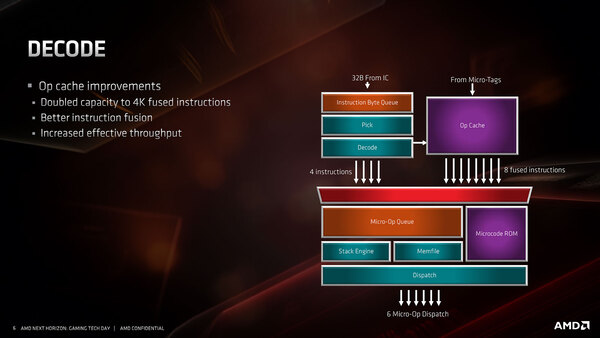

この15%のIPC改善はどうやって実現されたかという話であるが、まず基本的な構造が下の画像だ。

Zen/Zen+の構造と比較すると、以下の違いが挙げられる。

- AGUが1つ追加された3つになった

- Micro-op Cacheの容量が4Kopに倍増した

- 分岐予測に、新たにTAGE(TAgged GEometric)を利用した方式が追加された

そしてバッファ周りでは、以下の違いが挙げられる。

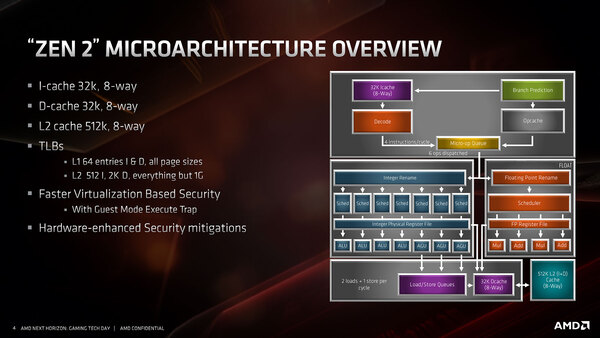

- L1 I-Cacheが64KB/4wayから32KB/8wayに変更

- TLBの大容量化(後述)

- 仮想化マシンのセキュリティー周りの高速化

- 脆弱性対策のハードウェアベースでの強化

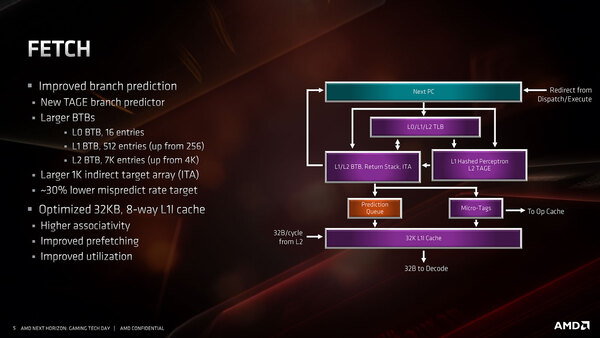

もう少し細かく見てみよう。まずはフェッチだが、BTBが大幅に強化されているのがわかる。もっともこれは上でも書いたが、従来のPerceptronベースの分岐予測に加えてTAGEベースの分岐予測も加わったことで、BTBのエントリーを増強しないと予測が収まりきらなかったものと思われる。他にITAのサイズを増やしたことも挙げられている。

インストラクションキャッシュ(L1 I-Cache)については、そもそもデータキャッシュ(L1 D-Cache)がやはり32K 8-Wayだったわけで、64Kの4-Wayがどこまで有効なのか不思議ではあったのだが、やはり思ったほど有効ではなかったということだろう。

2次キャシュとは32Bytes/サイクルで接続されており、これはデコード段の読み込み速度にあわせたものと思われる。

デコード段については大きくは変わっていないが、先に書いた通りMicro-op Cacheが4Kopに増量されたほか、Op-Cacheから最大8 Fused-opが出力されるようになった。またInstruction Fusionがさらに改良されたとしている。これらの結果として、実効スループットの改善がなされたと思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ