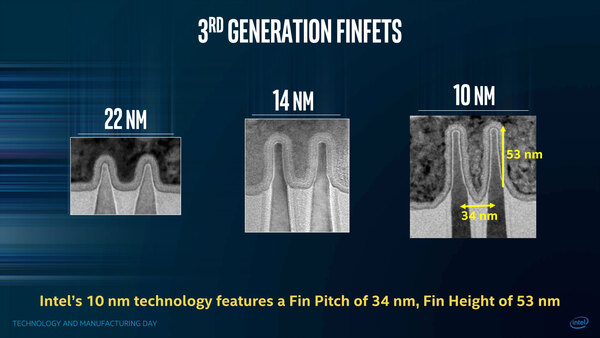

10nmではFinFETをより薄くより高くすることで

ダイエリアのサイズを稼ぐ

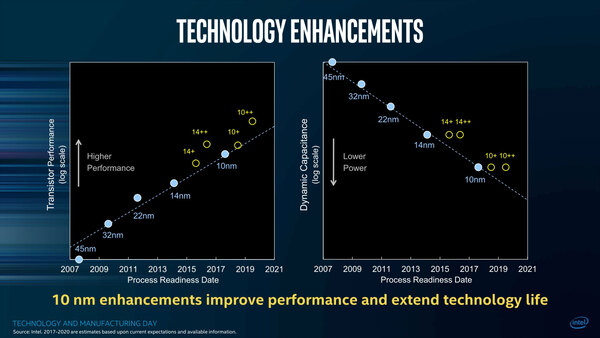

さて、次が10nm世代だ。インテルは、この世代でも3種類の派生型を提供する。10nm、10nm+、10nm++である。この10nm世代では、インテルはさまざまな改良を予定している。

同社は最近Hyper Scalingという言葉を使い始めた。これは「普通のScaling以上に微細化をする」という意味で、14nmについてもHyper Scalingだとしているが、10nmについても同様である。

まずFinFETそのものについては、より薄く、しかも高い方向に進化している。薄いだけでは駆動電流が減ってしまうので、その分高さを稼いだ形だ。

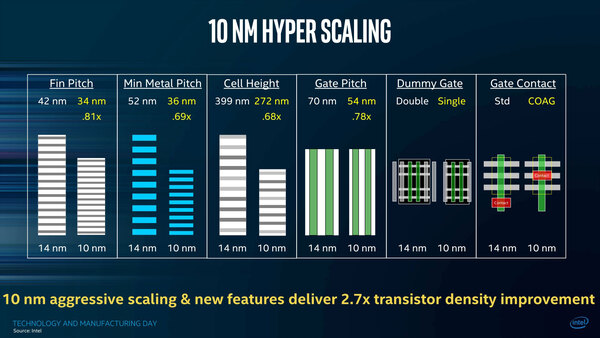

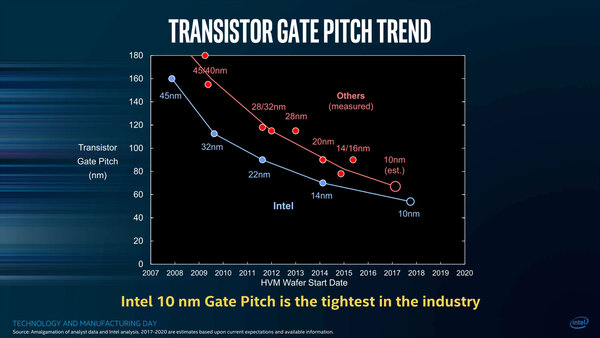

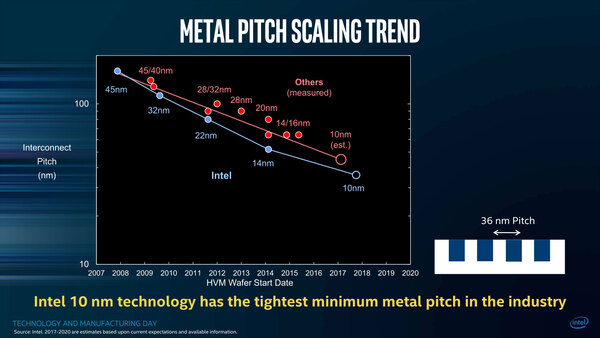

Gate Pitchは54nmまで縮小されており、これは他のファウンダリーのものと比較しても圧倒的に小さい、とする。

同様に、Metal Pitchも圧倒的に小さいとしている。

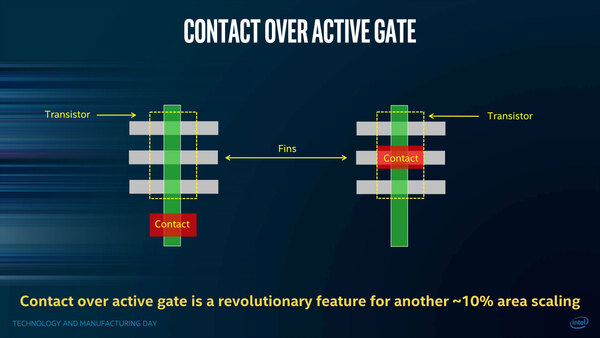

次はややわかりにくいが、Contactをどこに設けるかという話である。LSIでは一番下にトランジスタの層があり、その上に配線層を重ねていくが、そうなるとトランジスタと配線層を垂直な配線でつなぐ必要がある。

この垂直な配線がトランジスタにつながる部分がContactという部分で、従来だとこれはFinを外した場所に設けられていたが、10nmではこれをFinの真上に構成するようにした、という。

この技法そのものは以前から研究されており、FinFETに限らずプレーナ型のトランジスタでの研究もなされていた。インテルは2012年に、Contactに関していくつかの特許も取っている(例えばこれ)。

ただ実用化にあたっては、特に信頼性の問題が大きく、これまでなかなか実用化にこぎつけなかった。このあたりをどう解決したのかは不明だが、インテルは10nm世代でContactをFinの真上に構成する方式を全面的に採用するとしている。

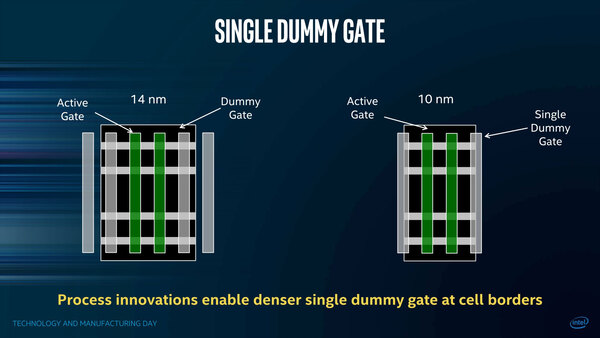

またCellの作り方にも手を入れた。従来、Cell Libraryでは両横のCellとの境界にDummy Gateを設けて敷居としていたが、10nm世代ではCellとCellの境界に1つだけDummy Gateを挟む形で、Dummy Gateの数をCellあたり1つ減らすことに成功したとしている。

このSingle Dummy Gate、これまでは特に複数Finのトランジスタの構成では、Finの中央の特性と一番端のDummy Gateに一番近いところで特性のばらつきが多く、これをカバーするのにDummy Gateをデュアルで入れるのが有効という話があったのだが、これをインテルはうまくコントロールすることでDummy Gateの数を減らせたということになる。

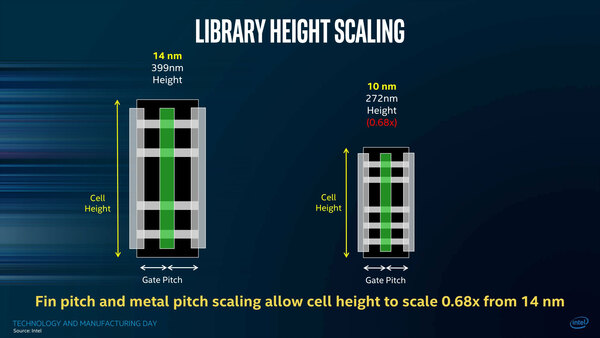

また、Cell Libraryの高さそのものも大幅に減らしたことで、エリアサイズを大幅に削減できたとしている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ