採用するプロセッサーのコアが決まったら

次は回路全体をつなぐバスの構造を決める

さて、前回のステップで、SoCを作る際のCPUコアが決まったとする。同じようなプロセスで、GPUコアも決まる。

ちなみにGPUコアの方はアーキテクチャーライセンスを提供しているところはないので、ARMの「Mali」、もしくはImagination Technologiesの「PowerVR」のどれかから選ぶというのが現実的な選択肢だ。

GPU IPとしては、例えば日本のDMP(Digital Media Professional)が提供するIPもあるが、あまりスマホやタブレットでの採用事例は聞かない。

このほかのケースとして独自GPUコアを用意するという案もある。例えばQualcommは「Adreno」という独自GPUを利用しているが、元々同社はAMDからImageonというGPUコアのIP供給を受けていたが、2009年にこのImageonを開発部隊ごと買収している。ちなみにImageonの元になったのはBitBoysの「Hammer」であるという話は連載157回で紹介している。

モバイル向けではないが、富士通は自動車向けに「Jade」と呼ばれる独自GPUを開発している。インテルもそうで、以前は「PowerVR」をベースにしていたが、最近は自社のGPUをベースにしている。ただCPUほどではないにせよ、GPUをゼロから作るのは大変で、普通はGPU IPを購入することになる。

話がまた逸れたので戻すと、CPU、GPU、メモリーコントローラーなどといった基幹部品に加えて、カメラ用のISPとインターフェース、液晶表示用の出力、さらにはUSBやI2C、SPIといった通信インターフェースや、ボタン/振動生成用モーターのインターフェースなど多様多種の回路を全部つなぎ合わせる必要がある。この際に、こうした回路全体をつなぐものが内部バスである。

この内部バスもいくつかある。もっとも有名なのが、やはりARMの提供する「AMBA」(Advanced Microcontroller Bus Architecture)と呼ばれるものである。このAMBAは1.0~4.0まで4種類のスペックが出ているので、表にまとめた。

| 「AMBA」のスペック | ||||||

|---|---|---|---|---|---|---|

| 高速インターコネクト | 高速バス | 低速バス | トレース | |||

| AMBA 1.0 | ASB | APB | ||||

| AMBA 2.0 | AHB | ASB | APB 2 | |||

| AMBA 3.0 | AXI 3 | AHB-Lite | APB 3 | ATB 1.0 | ||

| AMBA 41.0 | AXI 4 | AXI4-Lite | APB 4 | ATB 1.1 | ||

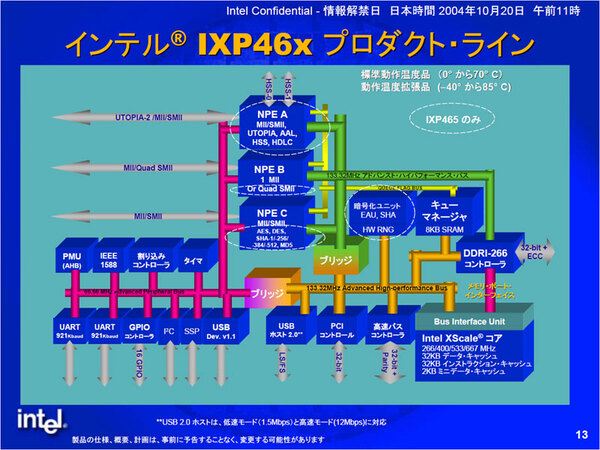

最初に登場したAMBA 1.0はASB(Advanced System Bus)とAPB(Advanced Peripheral Bus)であるが、これはあまり広く使われなかった。次に登場したのがAMBA 2.0で、ASBに加えてAHB(Advanced High-performance Bus)が追加され、これが広く利用されることになった。具体例として、モバイル向けでもなんもないので恐縮だが、大昔の「IXP46x」の構成を下の画像で示す。

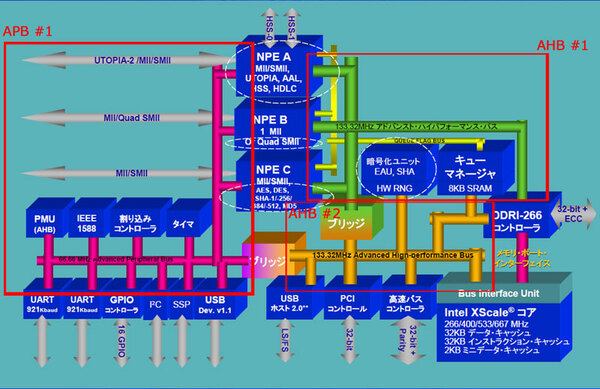

「IXP46x」は、右下にXScaleコア、中央上にパケット処理専用コプロセッサー、左下に周辺インターフェースが搭載されたネットワーク向けSoCである。ここでバスにあたるものを示したのが下の図である。

3種類のネットワークコプロセッサーとメモリコントローラーをつなぐAHB #1、XScaleコアとPCI/USB、メモリーコントローラーをつなぐAHB #2の2つのAHBがブリッジで接続され、さらに低速な周辺I/OデバイスをつなぐAPBがやはりブリッジでつながっている構造だ。

このAHB/APBの次に登場したのがAXI(Advanced eXtensible Interface)である。これはAMBA 1.0に準拠したもので、高速側にバスではなくファブリック形式の「AXI 3」を導入したのが大きな違いである。ただ従来型のインターフェースも必要ということでAHB-Liteと呼ばれるものも追加されている。

AHB/APBは名前の通りバスなので、例えば2つのCPUが同時にそれぞれ別のデバイスにアクセスすることはできない。これは特にマルチコアCPUなどでは性能低下の大きな要因であり、これを解決するためにファブリックを導入したのがこのAXI 3である。

AXI 3をさらに高性能化したのが「AXI 4」という最新のもので、大きな違いはキャッシュコヒーレンシ性の付加である。実際にはAXI4そのものはあくまでもファブリックの規格で、キャッシュコヒーレンシそのものはACE(AXI Coherency Extensions)と呼ばれる別の規格になっているが、ACEはAXI4への拡張なので、AXI4で追加されたとしても間違いではないだろう。

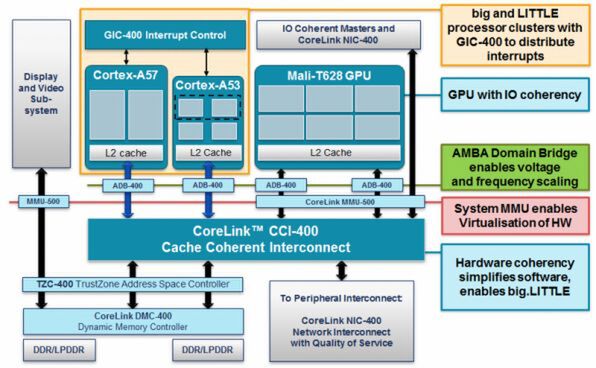

このAXIはさらに広範なマルチプロセッサー対応、例えばbig.LITTLEへの対応とか、HSAで要求されるCPUコアとGPUコアのキャッシュコヒーレンシ性などにも対応するものだ。

長々と説明してきたが、このAMBAやAHB/APB/AXIといった規格は、あくまで規格である。ただこれをやはりIPの形でARMは提供している。下の画像はARMが提供する「CCI-400」というインターコネクトのIPコアである。これを購入して突っ込むだけで、CPUやGPU、その他のサブシステムとの接続が完了するというわけで、こちらもCPUコアに劣らず重要なコンポーネントになっている。

ちなみにARMは、さらに大規模な構成に向けて「CCN-504」や「CCN-508」といったIPも用意している。また、CCN-400を使うまでもないほど小規模なシステム向けには、AMBA 2をベースとしたAMBAデザインキットを用意しており、こちらを使って簡単にインターコネクトが構築できる用意をしている。

ARM以外のバスを探す

ここまではもっぱらARMベースの話であったが、それ以外はないのかというとそうでもない。対抗製品はいくつかあるが、もっとも広く利用されているのは「OCP-IP」だろう。

OCPとはOpen Core Protocolの略で、OCP-IP Associationという業界団体がこの仕様を管理している。仕様はOCP-IP Associationから入手できるほか、多くのIPプロバイダーがOCPに対応したIPを提供している。

このIPの中には、OCPに対応した回路(CPU/GPU/メモリーコントローラーなど)のほか、OCPベースのバスやインターコネクトなど各種用意されており、こちらを使ってSoCを構築することもやはり可能である。

有名なところでは、Imaginationが提供するMIPSコアは原則OCP対応で接続になっている。ただしMIPS32 24Kなどの古いコアは、専用のブリッジIP経由となる。もっともOCP/AXIブリッジも多く存在するので、MIPSプロセッサーをAXIにつなぐことも技術的には可能である。

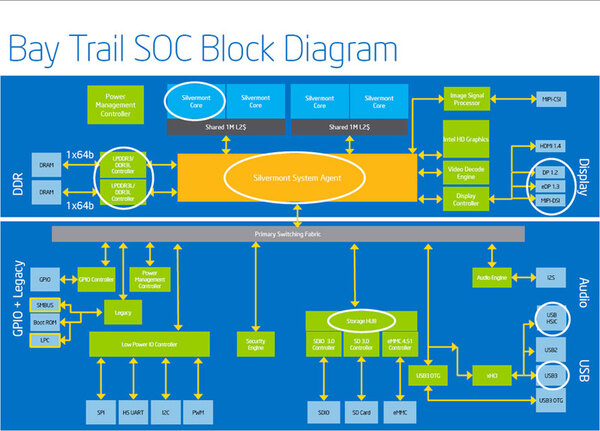

もっと頑なに、独自インターコネクトを使うところもある。代表例がインテルである。下の画像はBay Trail-Tの内部構造を示したものだが、CPUやメモリーコントローラは自社のIOSF(Intel On-chip System Fabric)ベースのもので、またプライマリーファブリックもIOSFベースのものとなっている。いくつかのIOSFに未対応な周辺回路のみ、IOSF/OCPブリッジ経由でOCP接続という態度だ。IOSFは以前連載第173回で解説したので、耳慣れない方はご覧頂ければと思う。

このように、CPUやGPUなどのコンポーネント以外にも、どんなバスを使ってそれぞれのコンポーネントをつなぐかもまた、SoCを作る際には選択する必要があるわけだ。このあたりは通常、CPUやGPUの選択と同時に行なう必要がある。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ