“メインフレームゆずり”のSPARCプロセッサ設計の秘密

SPARCプロセッサとメインフレーム、「京」の関係とは?

2013年08月14日 08時00分更新

プロセッサの開発体制とロードマップは?

――プロセッサの開発体制はどのようになっていますか。

SPARCプロセッサの歴史の初期に米HAL Computerという会社があり、富士通はそこで最初の世代のプロセッサを開発、完成させました。しかし、第2世代の開発からは日本での開発に移行しました。現在は、メインフレームのプロセッサ開発部隊がSPARCも同時に開発しています。

メインフレームのプロセッサは「RAS(信頼性、可用性、保守性)」を実現する技術、機能が充実しているのが特徴ですが、富士通ではこの強力なRAS機能をほぼそのままSPARCプロセッサにも組み込んでいます。同じ開発部隊が担当していることの強みですね。

競合各社のUNIXサーバ向けプロセッサと比較しても、富士通製SPARCプロセッサのRAS機能は充実したものとなっています。PCやワークステーション向けから発展してきたx86系などのオープン系プロセッサは、やはりチップレベルで高信頼性を実現する取り組みでは遅れている部分があります。たとえば、比較的故障率の高いキャッシュメモリなどを除けば論理回路にチェッカーがないのが普通であり、キャッシュメモリのチェッカも単純なパリティチェックのみで、エラーが発生したら止めるというレベルのものです。一方で、富士通のSPARCチップの場合はキャッシュに対してもECC(Error Checking and Correction)を付与しており、エラーを訂正したうえで処理を継続することが可能です。さらに、演算器にもチェッカーが付いている設計は“メインフレーム譲り”であり、富士通製SPARCはほかにはあまり例のない仕様となっています。

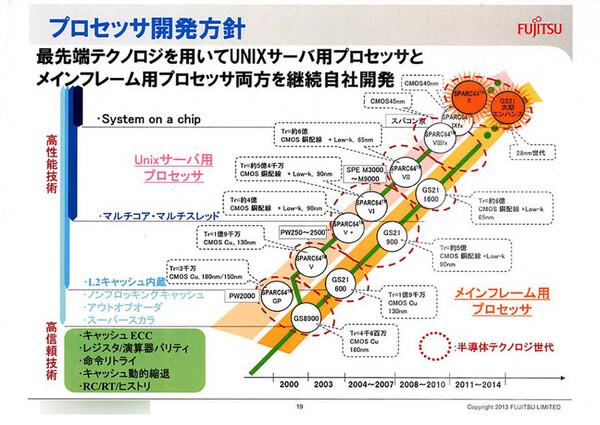

富士通のプロセッサ開発ロードマップでは、SPARCプロセッサとメインフレーム用プロセッサの関係も明示しています。これを見れば、SPARCプロセッサとメインフレーム用プロセッサが同じ半導体技術を共用していることがわかります。

たとえば、「GP7000Fシリーズ」が搭載していたSPARC64 GPプロセッサは、2000年に出荷を開始したメインフレーム「GS8900シリーズ」のプロセッサと同じ半導体技術を利用しています。また「PRIMEPOWERシリーズ」のSPARC64 Vプロセッサは、メインフレームのGS21シリーズが搭載するプロセッサと同じ半導体世代です。4月に発表した第10世代のSPARC64 Xプロセッサは28nmプロセスを採用していますが、これに対応するメインフレーム用プロセッサは来年(2014年)の発売予定で開発中です。また「京」などのスーパーコンピュータ向けプロセッサは、SPARCをHPC向けにカスタマイズしたものとなります。

これら3種類のプロセッサを開発するために独立した開発チームを3つ用意するのではなく、基本的には1つの開発チームで3種すべてのプロセッサを開発しています。もっとも、開発期間が重なる時期もあるため、チームの一部がSPARC64を、ほかのメンバーがHPC向けを、といった形になることはあります。

なお、現在でもSPARCの仕様は独立組織の「SPARC International」が管理していますが、アーキテクチャのアップデートに関しては64ビット化されたSPARC V9以降、目立った動きがありません。富士通ではSPARCプロセッサの命令セットを順次拡張しており、SPARC M10でもさまざまな専用命令を追加しました。SPARC Internatinal側でも新たな命令の追加を行うのではないかと思っていますが、V10という形でまとめるかどうかはわかりません。仮想化関連のアーキテクチャについても検討が行われているようです。

富士通からは、M10で拡張した命令セットをSPARC Internatinalに提案していますが、それが受け入れられるかどうかは不明です。

この連載の記事

-

第3回

サーバー・ストレージ

富士通とオラクルが目指すSPARC/UNIXサーバーの未来 -

第1回

サーバー・ストレージ

富士通はSPARC/UNIXサーバーをどう作ってきたか -

サーバー・ストレージ

富士通のUNIXサーバー、かく戦えり - この連載の一覧へ