Haswellのグラフィック性能を考察

そのHaswellだが、内部アーキテクチャーを説明するセッションの内容は、おおむね昨年秋のIDFで公開されたものとほぼ同じであり、内容はすでに紹介した連載169回と連載170回以上の新しい情報はなかった。ただ、GT3のグラフィックに関してのみ、新しい情報が出てきたので説明しよう。

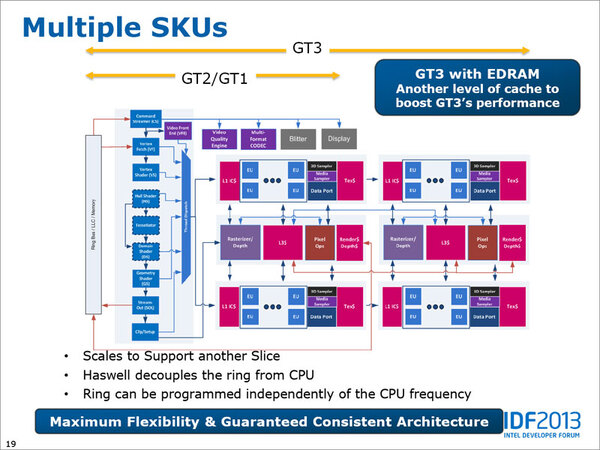

Haswellは、GPUの構成が3種類あり、それぞれGT1/GT2/GT3と呼ばれている。それぞれの違いは以前連載188回で紹介した通りで、GT1がローエンド、GT3がハイエンドとなるが、このGT3にはeDRAMを搭載するものがあることが明らかにされた。

下の画像がGT1/GT2におけるHaswellの構成であるが、GT3では新たにインターフェースが1つ追加になり、さらにeDRAMが別に搭載されることがわかる。情報はこれだけだが、ここからある程度構成を推察できる。

まずeDRAMと呼ばれるものの正体だが、これは本来の意味でのeDRAM(Embedded DRAM)ではなく、マルチチップモジュールの形で別チップで搭載されるDRAMと思われる。GDDR5あたりの特注品が搭載されるであろう。本来eDRAMと呼ばれる製品は、既存のCMOSプロセスにDRAMセルを作りこむというもので、国内だと東芝や旧NEC、海外だとIBMなどが得意としていたものである。

現在も、TSMC(Taiwan Semiconductor Manufacturing Company)などではこのeDRAMを一部のプロセスで提供している。この方式の場合、CPUなどのロジック回路とDRAMが同一のダイで構成され、レイテンシーも少なく便利な反面、eDRAMに結構なダイサイズを食われ、eDRAMがネックになって速度が上げられないなどの欠点もある。

最大の問題は、DRAM構造がネックになってプロセスの微細化が難しいというもので、少なくとも40nm未満のプロセスでこれを実現した例はない。これはインテルの22nmプロセスでも同様である。したがって、通常のDRAMを別チップの形で接続するほうがリーズナブルだ。特にGT3にeDRAMを持つバージョンと持たないバージョンがあるとすれば、別チップにするほうが製品の作り分けが簡単になるだろう。

これが通常のDDR3やGDDR5かというと、おそらく違うであろう。理由は2つあり、メモリバス幅はDDR3で最大16bit、GDDR5でも最大32bitでしかなく、これで速度を上げてもそれほど帯域は広くない。できれば64~128bit幅がほしいところだが、そんな標準品は存在しない。だからといって、複数個のDRAMチップを搭載できるほどパッケージは大きくない。

DDR3にしてもGDDR5にしても、基板上で2~4インチの配線を引き回し、それなりの出力を持つ駆動回路を前提にしているが、マルチチップモジュール方式だと配線は1インチにも満たない。そのため、もっと駆動力を小さくして、その分省電力化を図りたいが、これもまた標準品は存在しない。また、容量は数GBも必要なく、せいぜい128MBあれば十分だから、これもまた標準品では選択しにくい。

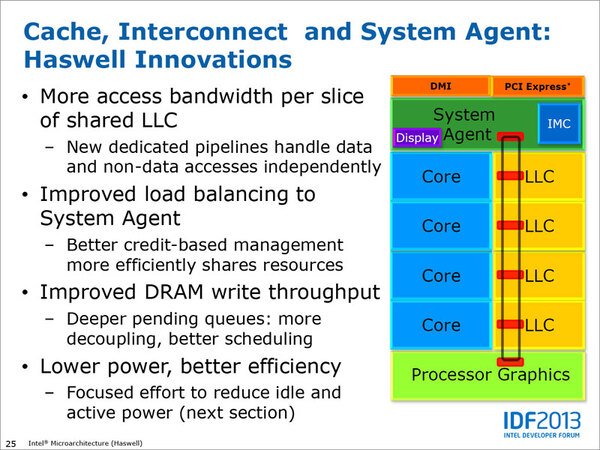

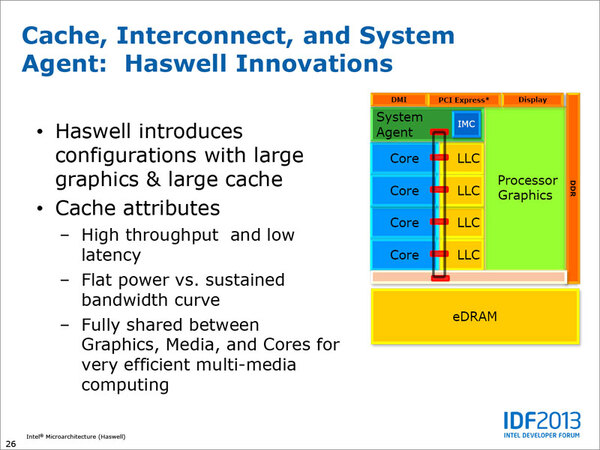

eDRAMの構成はともかく、おもしろいのはこのeDRAMがGPU向けのローカルフレームバッファだけでなく、CPUのキャッシュとしても動作することだ。下の画像をみると、DDRコントローラーと書かれたオレンジの部分が、ベージュ色の部分にも接触しているのがわかる。

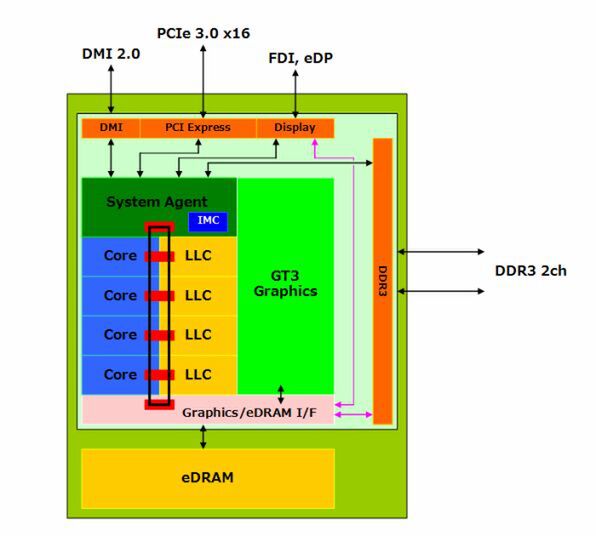

この画像を元に、いくつか省略されている部分を筆者の推定で追加したのが下図だ。

おそらくメモリーコントローラーはSystem Agentのみならず、Graphics/eDRAMインターフェースにも接続する構造になっているほか、ここからディスプレーへの出力パスも存在していると思われる。もちろんこれはeDRAMがフレームバッファ兼オフチップキャッシュとしても動作するという前提での想定であるが、大きくは外していないはずだ。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ