9月11日から13日まで開催された開発者向け国際会議「Intel Developer Forum San Francisco 2012」にて、インテルは次期プロセッサーである「Haswell」(ハズウェル)の詳細を発表した。今回は最新ロードマップ兼CPU進化論の最新版として、Haswellの詳細をわかる範囲で説明したい。

Sandy Bridgeをベースに

アウトオブオーダー部に手を入れたHaswell

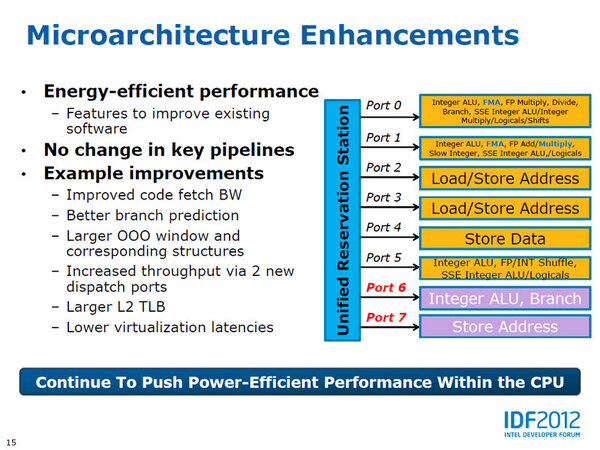

Haswellは現行の「Ivy Bridge」にも増して、低消費電力にフォーカスした製品であり、しかも性能の改善はもっぱらGPU側となっている。またHaswellの世代では、SoC(System On Chip)に向けた対応も大きな目玉であるが、CPUコアにもずいぶん手が入ったものになっている。

Haswell世代の大きな特徴は以下の6点にある。

- 8命令同時発行。これにあわせて内部のバッファを大幅に強化

- 分岐予測を強化

- AVX2命令を搭載

- トランザクション命令拡張を実装

- セキュリティー機能を拡張

- 仮想化状態における性能を改善

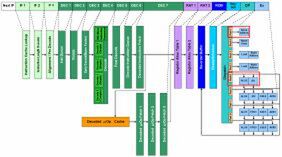

「Yonah」世代(Core Duo)で6ポートに拡張されたDispatch部は、その後「Merom」から「Nehalem」を経て「Sandy Bridge」と3世代に渡って利用されていた。これがついにHaswellで、8ポートに増強された。

新しく追加された2ポートは、「Port 6」が整数演算(Integer ALU)と分岐処理(Branch)に、「Port 7」がStore Addressに割り振られている。この結果、Haswell世代ではついに、同時8命令の処理が可能になった。またStore Addressもひとつ増えたことにより、メモリー書き込み性能も増強された。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ