2コア1パッケージのSmithfieldでは

E8500の意味がなくなる?

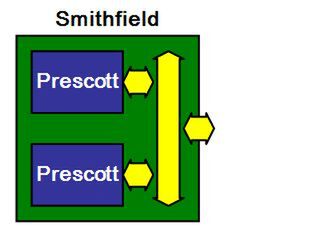

ここまでは力技で何とかできたのだが、SmithfieldのXeon MP展開ではつまづくことになった。Smithfieldは図3のように、2つのPrescottのFSBをパッケージ上の配線で結合するタイプのデュアルコアCPUである。インテルのロードマップでは、Prescottのデュアルコア化はバックアッププランで、本来は「Tejas」が投入される予定だった。

だが、Tejasは連載118回で説明したように自滅。一方でAMDは、Athlon 64のデュアルコア製品として、Athlon 64 X2やデュアルコアOpteronの準備を着々と進めていた。インテルにはなんらかの対抗策が必要であり、Smithfieldは「Core 2」シリーズが出るまでは、劣勢ながらなんとかAthlon 64 X2に対抗できた。

このSmithfieldをXeon MPに持ち込んだ場合どうなるか? それが図4の構造である。せっかくFSBを2本に増やしたにも関わらず、それぞれのFSBに4つずつCPUコアがぶら下がることになってしまい、667MHz駆動が不可能になってしまった。これでは何のためにE8500をわざわざ投入したのかわからない。

だからといって、Xeon MP系列にデュアルコアCPUを投入しないままでは、AMDのデュアルコアOpteronに後れを取ることは必至である。なにがなんでも、Xeon MP向けのデュアルコアCPUを投入しなければならない。

半年強でハイエンドから

滑り落ちたPaxville

前置きが長くなったが、Xeon MP向けのデュアルコアCPUを投入するために開発されたのが、今回のネタであるPaxvilleである。開発開始時期はおそらく、Tejasがキャンセルになった直後、2004年の第2四半期であろう。Tejasは単にデスクトップだけでなく、Xeon向けの展開も考えられていたから、これがキャンセルになったら代替製品が絶対に必要だ。Tejasの目的は、前掲の図1構成で利用できるデュアルコアCPUを、Prescottベースで開発することである。結果として、構成は必然的に決まってくる。

図5はPrescottとSmithfield、Paxvilleの構造をまとめたものだ。「BIU」とはBus Interface Unitの略で、ここからFSBが出てくる。PaxvilleはCPUコアと2次キャッシュはそれぞれ個別だが、BIUは2つのコアをまとめて共有している。これにより、図1の構成でも667MHz FSBで駆動できるデュアルコアCPUが構成できる。

理屈は簡単であるが、CPUコア/2次キャッシュはともかく、BIUに関しては完全に新規作成となる。おまけにサーバー向けプロセッサーの検証は、デスクトップ向けよりもはるかに時間を食う。登場まで1年以上かかるのは致し方ないところだ。先に「設計チームが大忙し」という話をしたが、あれらに加えてPaxville向けにBIUの新設計も行なっていたのだから、Core 2の開発が完全にイスラエル任せだったのも無理のない話である。

こうしてPaxvilleは、まず2005年10月にXeon DP向けの「Xeon 2.8GHz」としてリリース。2005年12月にはXeon MP向けの「Xeon 7020/7030/7040/7041」としてリリースされた。

この連載の記事

-

第803回

PC

トランジスタの当面の目標は電圧を0.3V未満に抑えつつ動作効率を5倍以上に引き上げること IEDM 2024レポート -

第802回

PC

16年間に渡り不可欠な存在であったISA Bus 消え去ったI/F史 -

第801回

PC

光インターコネクトで信号伝送の高速化を狙うインテル Hot Chips 2024で注目を浴びたオモシロCPU -

第800回

PC

プロセッサーから直接イーサネット信号を出せるBroadcomのCPO Hot Chips 2024で注目を浴びたオモシロCPU -

第799回

PC

世界最速に躍り出たスパコンEl Capitanはどうやって性能を改善したのか? 周波数は変えずにあるものを落とす -

第798回

PC

日本が開発したAIプロセッサーMN-Core 2 Hot Chips 2024で注目を浴びたオモシロCPU -

第797回

PC

わずか2年で完成させた韓国FuriosaAIのAIアクセラレーターRNGD Hot Chips 2024で注目を浴びたオモシロCPU -

第796回

PC

Metaが自社開発したAI推論用アクセラレーターMTIA v2 Hot Chips 2024で注目を浴びたオモシロCPU -

第795回

デジタル

AI性能を引き上げるInstinct MI325XとPensando Salina 400/Pollara 400がサーバーにインパクトをもたらす AMD CPUロードマップ -

第794回

デジタル

第5世代EPYCはMRDIMMをサポートしている? AMD CPUロードマップ -

第793回

PC

5nmの限界に早くもたどり着いてしまったWSE-3 Hot Chips 2024で注目を浴びたオモシロCPU - この連載の一覧へ