今回のCPU黒歴史は、インテルのXeon向けプロセッサーである「Paxville」である。と言っても「なんだっけ、それ?」という方も多いであろう、わりとかわいそうな位置付けのプロセッサーである。Paxvilleにまつわる問題は、以前に連載61回で少し触れているが、改めて説明したい。

Prescottのマイナーチェンジが

乱発されたPentium 4時代のXeon

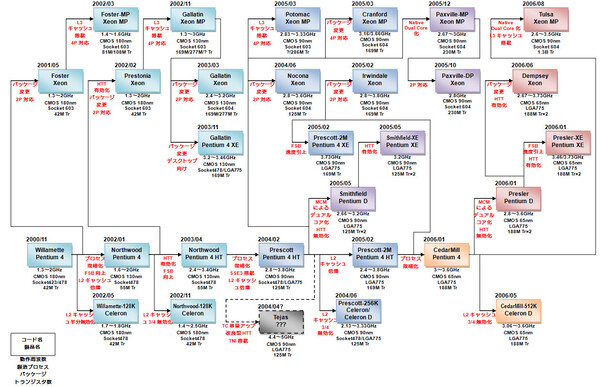

まずは連載38回に掲載した、2002年から2007年にかけてのサーバー向けロードマップをベースに、当時のXeon製品について説明しよう。インテルは2004年2月に、NetBurstアーキテクチャーベースで90nmプロセスを使った「Prescott」コアを、まずデスクトップ向けにリリースする。

当時のインテルは、デスクトップ向けとサーバー向けに同じコアを利用していた。2004年6月にはPrescottをそのまま利用した「Xeon DP」(デュアルプロセッサーシステム)向けの「Nocona」が投入される。だが困ったのは「Xeon MP」(4CPU以上のマルチプロセッサーシステム)向けである。

その前の世代では、Xeon MP向けに「Gallatin」コアが投入されていた。Gallatinは4プロセッサー構成にともなうFSB動作周波数の低さを補うべく、最大4MBの3次キャッシュを搭載したモデルであった。ところがPrescottやNoconaの2次キャッシュはわずか1MBで、もちろん3次キャッシュは搭載していない。このままでは動作周波数こそ多少引きあがるものの、3次キャッシュを搭載しないことで、むしろ性能的には落ちかねない。

これは由々しき事態であるということで、インテルはPrescottをベースに、大容量3次キャッシュを搭載したコアを製造することになる。これは2005年3月に、最大8MBの3次キャッシュを搭載した「Potomac」コアとしてXeon MP向けに投入される。これとあわせて2005年3月には、3次キャッシュを搭載しない、つまりPrescottそのままのCPUを「Cranford」コアとして発表している。

実はインテルはこの時、デスクトップ向けにも2次キャッシュ容量を倍増させた「Prescott-2M」を開発していた。これは1ヵ月前の2005年2月に、モデルナンバーだけを変えたPentium 4として、追加投入されている。さらに、このPrescott-2MをXeon DP向けにした「Irwindale」も、同じ2005年2月に投入された。

これらに加えてデスクトップ向けには、PrescottコアをMCM※1構成で2チップ乗せた「Smithfield」も同時に開発しており、これは2005年5月に「Pentium D」として投入された。

※1 Multi Chip Moduleの略で、1パッケージ内に複数のダイを重ねて封入するパッケージ構成。

Pentium 4系列を担当していたインテルのオレゴン設計チームは、この時期には壮絶に忙しかったであろう、ということは容易に想像がつく。CPUのパイプラインそのものは特に変更がなく、いずれも純粋に2次/3次キャッシュの容量を変えるだけではある。しかし1MB 2次キャッシュと2MB 2次キャッシュ、1MB 2次キャッシュ+4MB/8MB 3次キャッシュという3種類のダイが存在し、さらに1MB 2次キャッシュのダイのMCM構成もあった。ダイの変更は当然物理設計の手直しをともなうし、Pentium 4向けとXeon DP向け、Xeon MP向けでは検証のレベルも変わってくるから、検証チームも大忙しである。

ところでこの時、Xeonには2種類のパッケージが存在した。「Socket 603」と「Socket 604」である。実のところ電気的に両者は同一で、Socket 603対応のCPUはSocket 604に装着できるが、Socket 604対応のCPUはSocket 603には装着できなかった。ようするにダミーピンが1本追加されたのがSocket 604である。両社の差はFSBの違いによるものだ。Socket 603は400MHz FSBに限られていたが、Socket 604はもっと高速に動作させられた(技術的には最大1066MHz)。実際に製品として実現されたのは、800MHz FSBが最速ではあったが。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ