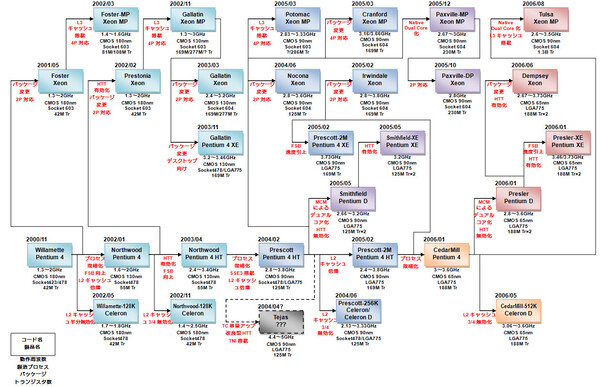

CPU黒歴史第5弾は、インテルの90nm世代の話である。「Willamette」に始まり、「Northwood」でそれなりに性能と消費電力のバランスも取れて、しかも動作周波数を上げやすいということで比較的好評だった「Pentium 4」シリーズ。これに大ブレーキをかけたのが「Prescott」世代である。連載61回でも一度説明したが、まずはこのPrescottの話から始めよう。

大幅な機能拡張と高速化の工夫を

凝らしたPrescott

NorthwoodからPrescottへの改良点として、当初インテルから挙げられたのは以下のような内容であった(関連記事)。

- 90nmプロセスを利用し、さらに「歪みシリコン」を利用することで高速化を図る。

- 内部配置を大幅に見直すことでクリティカルパスを大幅に短縮し、より高速動作を可能にした。

- 1MBの2次キャッシュを搭載。

- 「PNI」(Prescott New Instruction)こと「SSE3」と呼ばれる新しい13命令を搭載したほか、既存の命令に関してもいくつか高速化を施した。

しかし、実はこれだけではなかった。というよりも、この程度の改良であれば、パイプラインが20段から31段にまで増える理由はない。Prescottは後追いの形で、以下の機能を実装していた。

- Intel VT(Vanderpool Technology)

- Intel IA32e(Yamhill Technologyの派生型、現在のIntel 64)

- Intel TXT(LaGrande Technology)

厳密に言えば、Intel TXTはPrescottや後継の「CederMill」の世代では結局サポートされなかったのだが、実装されたのはこの時期だった。これらの拡張をサポートするために、Prescottでは長大なパイプラインが実装されることになったのである。

この連載の記事

-

第781回

PC

Lunar LakeのGPU動作周波数はおよそ1.65GHz インテル CPUロードマップ -

第780回

PC

Lunar Lakeに搭載される正体不明のメモリーサイドキャッシュ インテル CPUロードマップ -

第779回

PC

Lunar LakeではEコアの「Skymont」でもAI処理を実行するようになった インテル CPUロードマップ -

第778回

PC

Lunar LakeではPコアのハイパースレッディングを廃止 インテル CPUロードマップ -

第777回

PC

Lunar Lakeはウェハー1枚からMeteor Lakeの半分しか取れない インテル CPUロードマップ -

第776回

PC

COMPUTEXで判明したZen 5以降のプロセッサー戦略 AMD CPU/GPUロードマップ -

第775回

PC

安定した転送速度を確保できたSCSI 消え去ったI/F史 -

第774回

PC

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今 -

第773回

PC

Sound Blasterが普及に大きく貢献したGame Port 消え去ったI/F史 -

第772回

PC

スーパーコンピューターの系譜 本格稼働で大きく性能を伸ばしたAuroraだが世界一には届かなかった -

第771回

PC

277もの特許を使用して標準化した高速シリアルバスIEEE 1394 消え去ったI/F史 - この連載の一覧へ