4プロセッサーシステム向けの

新チップセットIntel E8500

この当時、1・2プロセッサーシステム向けのXeon DPは、積極的にSocket 604に移行していったが、4プロセッサーシステム向けのXeon MPは依然として、Socket 603のままだった。そのため、大容量3次キャッシュを搭載したPotomacが低速なSocket 603のままな一方で、PrescottそのままのCranfordはSocket 604に対応するというあべこべな状況にあった。

もっともインテルとしても、いつまでもXeon MP系列を400MHz FSBのままに留め置くつもりはなかった。いくら大容量3次キャッシュを搭載したからと言っても、キャッシュミスが発生したらメモリーアクセスが必要であり、そこでFSBの遅さがボトルネックになるからだ。そこでインテルはこのPotomac/Cranfordの発表にあわせて、新しく667MHz FSBに対応したXeon MP向けのチップセットとして、「Intel E8500」シリーズを投入する。

E8500は図1に示すような、かなり大規模なものである。「E8500 NB」(North Bridge)から2本のFSBが出て、それぞれ2プロセッサーずつのXeon MPと接続される。メモリーコントローラーは「E8500 XMB」(eXternal Memory Bridge)と呼ばれるチップが別に用意され、このE8500 XMBとE8500 NBは、「IMI」(Independent Memory Interface)と呼ばれる専用バスで接続される。

E8500 XMBはDDR-266/333とDDR2-400に対応し、それぞれが2チャンネルのメモリーバスを持ち、1チャンネルあたり最大4枚のDIMMを装着できる。I/OとしてはPCI Expressを合計36レーン持ち、それとは別にICH5を接続するための「HubLink」も搭載するという、実に重厚な構成である。

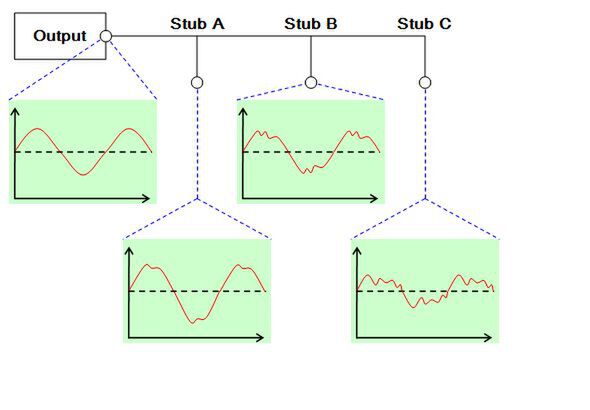

ここで重要なのは、E8500でついにFSBを2つに分割したことである。これは共有バス方式を取るFSBの限界が、露呈してきたからだ。一般論であるが、例えば図2のように、ある出力端子の先に配線が伸びて、「Stub A/B/C」という端子が用意されているケースを考える。

配線長や信号の振幅、周波数などによって程度は変わるが、出力端子の出ているポイントでは綺麗な波形になっていても、Stub A/B/Cで信号波形を測定すると、波形がどんどん崩れるし、信号の振幅もどんどん減っていくという状況になる。

これがPCI位の電圧(3.3V)と周波数(33MHz)ならば、Stubが15点程度まで耐えられるのだが※2、FSBは電圧※3、周波数(400~1600MHz)ともにタイトである。そのためCPUが2つまでならば、最終的に1600MHzまで引っ張ることができたが、CPUが3つ以上だと400MHzあたりで頭打ちになってしまった。これがXeon MPでFSBが低く抑えられていた理由である。

※2 PCIスロットの場合は1スロットが2Stubと数えるので、最大7スロットになる。

※3 AGTL+の場合、電圧そのものは0.8Vだが、振幅は±0.05V。

この問題を短期間でどうにか解決するのは大変に難しい。そこでFSBを2つに分けて、1本のFSBにCPUが2つずつぶら下がるようにすれば、400MHzの壁を越えてFSBを引き上げることが可能になる。事実、Potomac/CranfordベースのXeonは667MHz FSBで製品化されている。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ