伝送路速度アップと効率化で2倍の性能に

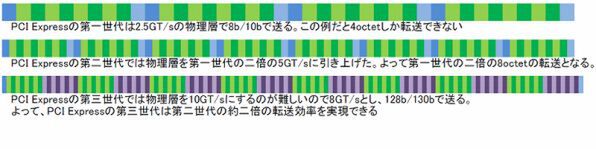

ではPCI Express 3.0は、いかにして物理層の転送速度を上げずに実効転送速度を上げたのか? それは「シリアル転送のブロック」を大きくすることで実現している。Gen2までのPCI Expressでは、8bitのデータを10bitのデータに変換する「8b/10b変換」でやり取りしていた。シリアル転送は本来、データとともに基準となるクロックが必要となるが、8b/10b変換をすることで転送効率が80%になる代わりに、クロックとデータをまとめて送れるようになる。

それに対して3.0では、128bitのデータを130bitに変換する128b/130b変換でやり取りする(図1)。つまりGen2までの方法だと128bit(16オクテット)のデータをやり取りするためには、物理層に160bitのデータを送る必要があった。それが3.0では130bitと、必要なビット数を減らすことによって、トータルで約2倍にしたというわけだ。

例えがイマイチかもしれないが、「走行速度を2倍にするのは難しいので、小型トラックから大型トラックに代えて運搬効率アップ」を実現したのがPCI Express 3.0、と思うといいだろう。

なお、ここまでGT/秒という単位を使ったが、これは物理層の周波数とデータ転送速度が8b/10b変換や128b/130b変換のために違うので、GHz単位の周波数とは一致しないからだ。Gen1では2.5GHz、Gen2では5GHz、3.0では8GHzの基準周波数が使われている。

メインメモリー以外のインターフェースは

シリアル化が完了しているが……

さて、現代のパソコンのインターフェースは、ほとんどがパラレル方式からシリアル方式に代わっている。これは標準化と高速化のためと言ってもよいだろう。パソコンで最初にシリアル化されたメジャーなインターフェースと言えば、「USB」(1996年に仕様発行)だろう。こちらは「複数の外部インターフェースを共通化したい」という発想から生まれたが、高速化によって外部ストレージ用としても使われている。

ディスプレーインターフェースに関しては、「DVI」や「HDMI」、「DisplayPort」などが使われているし、内部ストレージもシリアル転送の「SATA」や「SAS」が使われている。今回取り上げたPCI Expressも、その前にはパラレル転送の「PCI」バスだった。

パラレル転送でも高速化は不可能ではないが、ひとつ問題がある。複数ビットのデータを同時に到着させなければならないので、高速化すると配線長が問題になるのだ。例えば、手持ちのマザーボードを見てほしい。メモリーコネクターの周りを見ると、妙にウネウネとしたパターンが這い回っていることに気づくだろう。これは配線長をそろえるために設けられている。

パソコン用のメインメモリーとしてシリアルバスを採用した「RDRAM」もあったが、こちらの記事にあるとおり、結果的には失敗してしまった。しかし低容量のメモリーでも転送能力が高いシリアル転送メモリーは、主にゲームコンソールで使われており、現在もプレイステーション3で「XDR DRAM」が使われている。

この連載の記事

-

第12回

PC

「レアアース」モーターからガラスまで PCにも重要な資源 -

第11回

PC

「IMES」建物内のどこにいるかまでわかる位置情報技術 -

第10回

PC

「MRAM」NANDフラッシュを置き換える?新不揮発メモリー -

第9回

PC

「IEEE 802.11ac」Gbps級の速度を実現する新無線LAN規格 -

第8回

PC

「GeForce GRID」最新3D CGゲームがクラウド上で遊べる? -

第7回

PC

「熱アシスト記録」1プラッタ1.5TB超を実現するHDD記録方式 -

第6回

PC

「マグネシウム・リチウム合金」軽量LaVie Zを実現した新素材 -

第5回

PC

「ゴリラガラス」スマホを包む化学強化ガラスの秘密 -

第4回

PC

「インセル型タッチパネル」スマホを薄型化するセンサー -

第3回

PC

「MCP」大容量microSDHCに欠かせない高密度実装技術 -

第2回

PC

「Kepler」省電力と大幅性能向上を実現したNVIDIAの新GPU - この連載の一覧へ