Sandy Bridgeに続くリングバス構造を採用した

Nehalem-EXことXeon 7500

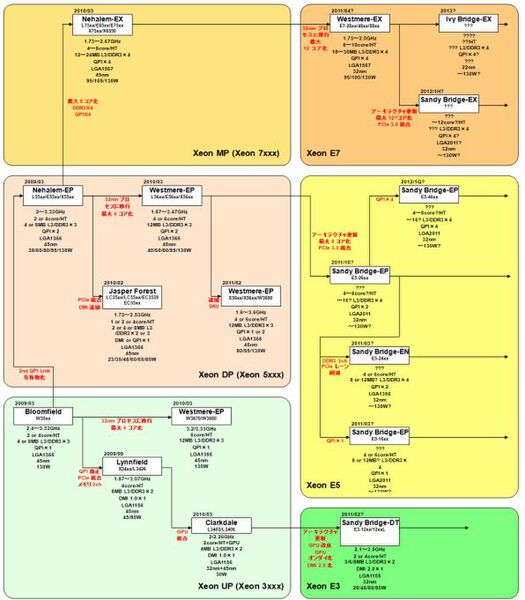

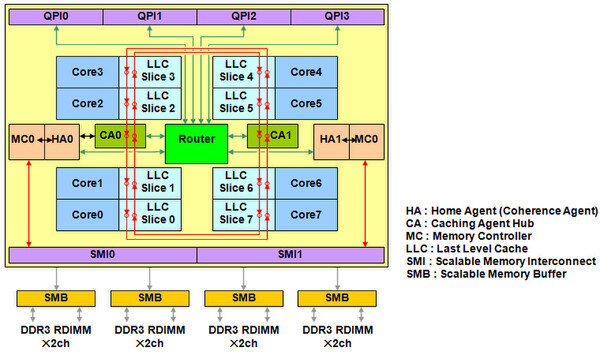

2010年3月には、ハイエンド向けの「Nehalem-EX」こと「Xeon 7500」シリーズも投入されている。この製品はNehalemをベースにしているのだが、最大8つのコアと2ブロックのメモリーコントローラー、さらに4本のQPI Linkと8ブロックに分散された最大24MBの3次キャッシュを、二重構造になったリングバスでつなぐという重厚な構成であった。メモリーはCPUの外に用意されたメモリーハブ(SMB)を経由して、最大8チャンネル分のメモリーが利用できるというお化けCPUである。

もっとも、この世代のリングバスはパフォーマンスなどの観点で、必ずしも成功したとは言いにくい。だが、このアイデアは次のSandy Bridgeで生かされることになったから、無駄とも言い切れないところだ。

Xeon 7500シリーズは、全製品が2010年3月に発表されており、小出しの追加製品はない。用途を考えると、Xeon 7500はもっぱらエンタープライズ向けである。エンタープライズ向け製品はOEM先がシステム検証にかなりの時間をかけることを考えると、後追いでぽろぽろと製品を出されても、OEMが困ってしまうからだろう。

メモリー容量だけを考えれば、このXeon 7500シリーズはHPC(High Performance Computing)にも向いていると言える。だが、メモリーアクセスのレイテンシーがNehalem-EPと比べて大幅に増えているために、科学技術計算などにはむしろ向かないと判断されたのだろうか。これを使ってHCPクラスタを組んだ例は、ほとんどない。

PCIeとQPI、DMIまで装備する変わり種CPU

Jasper Forest

話をXeon 5000シリーズに戻す。2010年2月に、インテルは通信機器向けとして「Jasper Forest」というコード名で呼ばれる製品群を投入した。このシリーズは、BloomfieldとLynnfieldの折衷というか、ちょっと複雑な構成である。

ベースとなるのはDP向けのNehalem-EPで、メモリーチャンネルも3チャンネル分が装備されているが、それとは別にPCI Expressが内蔵されている。チップセットとの接続はQPIとDMIの両方のモデルが用意されており、どちらを使うかはシステム構成により変わる。

ここで面白いのは、Jasper ForestではPCI Expressを使ってのDP以上の構成も可能なことだ。これは通信機器向けにはしばしば要求される構成である。そのためこれに合うように、BloomfieldにPCI ExpressとDMIを追加したのがJasper Forest、というわけだ。

さらにJasper Forestが面白いのは、ほかにはこの構成を使う製品がないという点だ。もちろん、PCI Expressを無効にすればNehalem-EPやBloomfieldになるし、逆にQPIとメモリーを1チャンネル無効にすれば、Lynnfieldにも転用が(技術的には)可能だ。しかし登場時期から考えると、そうした転用はしていないだろう。

そんなわけで、Jasper Forestコアは「Xeon xCx500」専用の製品となっている。「この改良は出荷数量面で割りに合うのか?」がちょっと謎だったが、Westmere系で更新される話も聞かないので、これはこれで帳尻があっているのかもしれない。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ