Katmai→Coppermine→Tualatinと続いたPentium III

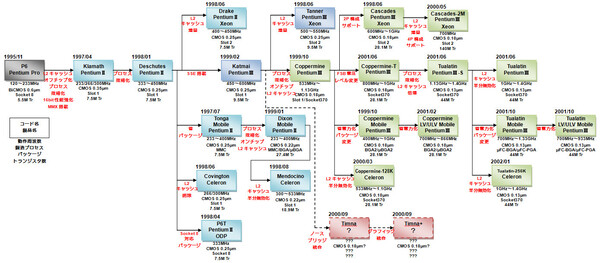

MendocinoコアのCeleronがDeschutesに性能面で肉薄してしまった問題に対応するために、インテルは1999年2月に、拡張命令「SSE」を搭載した「Katmai」コアの「Pentium III」をリリースする。これで(パイプライン段数増加の効果もあり)600MHzまで動作周波数を引き上げた。

さらに同年10月には、0.18μmプロセスを採用した「Coppermine」コアのPentium IIIをリリースする。このCoppermineでは、ついに2次キャッシュをオンチップ化することに成功。そうなるとカートリッジ形状で提供する必要がなくなるので、新しく導入されたパッケージが「Socket 370」である。ただし、いきなり全量切り替えてしまうと既存のユーザーの切捨てになるため、当初CoppermineはSlot 1とSocket 370の両パッケージでリリースされた。

ちなみに、Katmaiをベースに「Pentium III Xeon」(Tanner)がリリースされるが、これは「Drake」(Deschutesのキャッシュ増量版Pentium II Xeon)同様に、2次キャッシュを大容量化してSlot 2に移行したものだ。

またKatmaiをベースに、ノースブリッジまでワンチップ化して低価格向け製品を狙った「Timna」や、そこにグラフィックス機能も統合した「Timna+」も開発が始められていた。しかし、これらは2000年9月に計画が中止される。最大の要因はメモリーシステムにDirect RDRAMを利用しようとしたこと。Direct RDRAMを使うとシステムコストが全然下がらない(むしろ上がる)ので、差別化できないと判断されたためだ。このTimna/Timna+の開発はイスラエルのデザインセンターが担当しており、彼らはこの時の知見を、のちのPentium Mの開発に生かすことになる。

話を元に戻すと、このCoppermineもまた、多くの製品が登場することになった。まず、Xeon向けには「Cascades」が投入されるが、これは2プロセッサー対応を有効にしただけで、中身はCoppermineそのものである。ただし、これでは4プロセッサー構成以上には使えないため、Cascadesの2次キャッシュを2MBまで増量した(Coppermineは256KB)「Cascades-2M」を2000年にリリースする。

ちなみに、Coppermine/Cascadesのダイサイズは100mm2台だが※1、Cascades-2Mのダイサイズは375mm2に達している。またCascades-2Mの2次キャッシュを半分殺した「Cascades-1M」も同時にリリースされている。

※1 ステッピングによってダイサイズは若干異なり、当初は106mm2だったが、最終的には100mm2まで縮小している。

またモバイル向けには、Coppermineをそのままの形で「Mobile Pentium III」としてリリースした。さらに、Transmetaの「Crusoe」対抗のために、Coppermineから省電力でも動作する選別品を「低電圧版(LV)Mobile Pentium III」「超低電圧版(ULV)Mobile Pentium III」として、ラインナップすることになった。また低価格向けには、Coppermineの2次キャッシュを半分無効化した「Coppermine-128K」が2000年3月にCeleronとしてリリースされている。

これに続いて、インテルは0.13μmプロセスへの移行を予定するが、この0.13μmプロセスではFSBの信号レベルを、従来の1.5Vから1.25Vに引き下げる必要があった。そこで機械的形状は変えないまま、新しい1.25VのFSBを用意した。違いを区別するために、従来の1.5V対応ソケットが「Legacy PGA370」、新しい1.25V対応のものは「Flexible PGA370」と称するようになった。

後方互換性は維持されたので、Flexible PGA370に対応したマザーボードは1.5V対応のCPUも利用できた。しかしLegacy PGA370対応マザーボードは1.25V対応のCPUが使えないので、ちょっと厄介な状況になった。この移行をスムーズに行なうため、Coppermineコアのまま信号レベルを1.25Vに落とせるようにしたのが、2001年6月に登場した「Coppermine-T」だ。同時に、0.13μmプロセスに移行した「Tualatin」コアのPentium IIIおよびサーバー向けCPUの「Pentium III-S」もリリースされる。

この2001年というのは、インテルがPentium 4を発表した時期でもある。というのも、2000年3月にインテルとAMDは「どちらが先に1GHz駆動のCPUをリリースするか」で争った挙句、僅差でAMDの「Athlon」に先を越される羽目になった。また、0.18μmプロセスでは最大1.13GHzまで達するものの、動作が不安定なために回収される騒ぎになっていた。こうしたことを受け、インテルはメインストリーム向け製品をPentium IIIからPentium 4に切り替えることを決断する。

こうした動きを受けて、Coppermine-TやTualatinはむしろ「Pentium 4の普及の妨げになる」と判断されたのか、積極的に販売する方向に向かわなかった。Coppermine-Tは(信号電圧を1.25Vに下げられるにも関わらず)1.5V駆動としてリリースされたし、Tualatinも2次キャッシュを倍増したものは、サーバー向けのPentium III-Sとしてリリースされただけ。デスクトップ向けには2次キャッシュ容量を半分に減らした形でリリースされる。

もっとも、モバイルおよび組み込み向けには、その後も長くTualatinが使われた。Pentium 4の消費電力と発熱は、到底モバイルや組み込み向けに耐えられるものではなかったからだ。結果として、2003年にPentium Mが登場するまでの間、TualatinベースのMobile Pentium IIIは使われ続けた。その意味では、P6直系のアーキテクチャーは1995年から2003年まで、8年に渡って使われ続けたことになる。

今回のまとめ

・商標の問題もあり、名称を「Pentium」と改めた「P5」コアの新CPUは93年に登場した。CPU性能は強化されたものの、初期はチップセットに足を引っ張られたり、バグの発覚で回収騒ぎになったりと難産だった。

・MMX PentiumでPentium世代の足場を築いたインテルは、95年に「Pentium Pro」を投入する。16bitコードの処理性能の低さやコストの高さから、デスクトップPC分野では苦戦するも、サーバー分野では長く使われた。

・コストを下げて性能を上げたPentium II世代は、低価格路線CPU「Celeron」の登場や、キャッシュを一体型にした「Coppermine」コアの登場で、P6アーキテクチャー普及の立役者となった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ