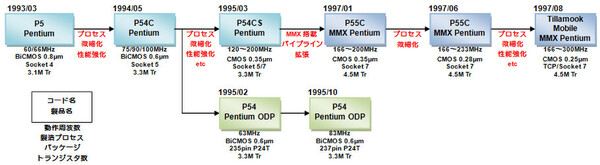

インテルプロセッサーの歴史を振り返る前回では、i4004から486世代までを一気に解説した。続く今回は「P5」、つまりPentium世代について語ろう。

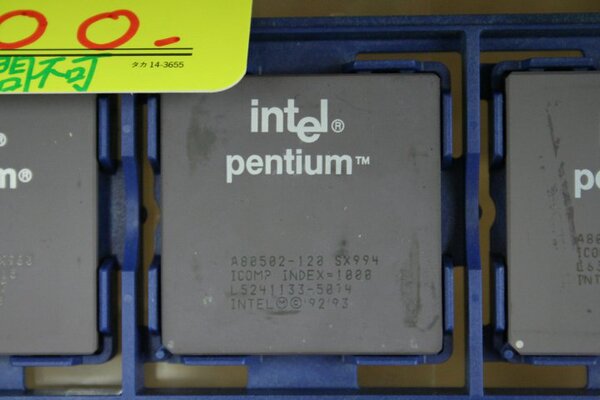

後に一世を風靡するPentiumも、

出だしはチップセットやバグで悩まされる

話は486時代にさかのぼる。当時、インテルは486世代に磨きをかけて、プロセスの微細化やライトバックキャッシュの搭載やらと、さまざまな手法で性能向上を図ってきた。しかし、競合メーカーも負けてはいない。特に486世代の場合、AMDやCyrix、IBMにTI(Texas Instruments)、UMCといったプロセッサーベンダーが486互換CPUを出荷していた。しかも、いくつかのベンダーは先んじて「586」の名称を使った製品を投入してきた。

これに関してインテルは、386の時代にも商標侵害として訴訟を起こしたりしたものの、1991年に「386の名称は広く浸透しており、商標とは認められない」という判断が裁判所でくだされてしまう。この結果、386のみならず486や586という名称も、互換メーカーが合法的に利用できることになった。こうした理由もあって、インテルは486の後継に586ではなく、「Pentium」という名称をつけることにした。

そのPentium、内部的には2イシューのスーパースカラー構造となっている。といっても完全な2イシューではなく、メインパイプライン(U-Pipeline)は全命令を実行できるが、サブパイプライン(V-Pipeline)は主要かつ簡単な命令のみ、という不完全な2イシューであった。とは言え、これでも大幅に性能は改善している。加えて「ハーバードアーキテクチャー」を採用し、命令キャッシュとデータキャッシュを分離した上で大容量化した。さらにはFPU(浮動小数点演算ユニット)も高速化されるなど、さまざまな点で性能は強化された。

ところが最初のP5に関しては、むしろチップセットで足を引っ張られた。それが「82430LX」、通称「Mercury」である(関連記事)。82430LXはとりあえずPCIバスをサポートしたものの、肝心のDMAバスマスタが動かずPIOモードのみのサポートとか、VL-Busに未対応なので高速な拡張カードがほとんど利用できないとか、そういった問題が多かった。

P5はコスト面でも、低価格な486ベースのシステムには太刀打ちできなかった。Intel DX4+VL-Busのシステムと比較すると、プラットフォーム全体の性能ではむしろ劣ったケースすらあったから、普及するはずもない。ただこれも、1994年に「P54C」コアのPentiumが投入されることで大分雰囲気が変わってきた。

ちなみにこのP54Cコアというのは、有名な「FDIVバグ」を引き起こした製品でもある。一時期は「返品だリコールだ」と大騒ぎになったこの世代が、最終的には486世代からPentiumへの移行を決定付ける世代になったわけで、世の中どう転ぶかわからないものである。

このP54Cコアを利用し、ソケット形状を486まで利用された「P24T」に変換した「Pentium ODP」(Over Drive Processor)などが既存の486ユーザー向けに投入されたりもした(当初は25MHz×2.5=62MHzの製品で、のちに33MHz×2.5=83MHzも登場)。

だが、本命となるのは1995年に投入された「P54CS」と、これにMMX命令を付加した「P55C」こと「MMX Pentium」である(関連記事)。プロセスの微細化と相まって、大幅に動作周波数を上げたこともあり、486との性能差は大きく開き、このあたりで主流はPentiumに移行することになる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ