ロードマップでわかる!当世プロセッサー事情 第800回

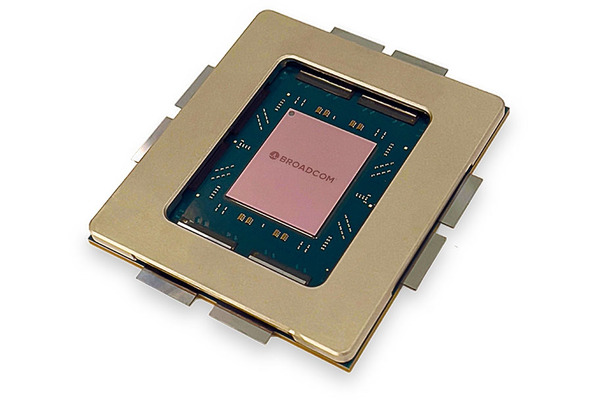

プロセッサーから直接イーサネット信号を出せるBroadcomのCPO Hot Chips 2024で注目を浴びたオモシロCPU

2024年12月02日 12時00分更新

2週間空いてしまったが、再びHot Chipsの話に戻ろう。今回取り上げるBroadcomはCPUでもGPUでもNPUでもない。というか演算の話ではなく、インターコネクトの技術である。今年のHot Chipsでは、Broadcomとインテル、それとTeslaがインターコネクトの技術に関する発表を行なった。

このうちTeslaに関しては、物理層はイーサネットながらその上のプロトコルをDojo同士の通信に最適化したという話で、「Hot ChipsよりHot Interconnectsでやりなさい」という内容であった(それを言えばBroadcomとインテルもそうなのだが)。

これはこれでおもしろかったのだが、マニアックすぎるので割愛して、Broadcomとインテルの方を説明したい。ということで今回はBroadcomのCPO(Co-Package Optics)の話である。

光学インターコネクトにおいては

電気信号の遅さが問題になる

Package Opticsに関しては、連載676回のLightmatterの際に少し触れた。もっともLightmatterの場合、演算そのものを光ベースで行なっている関係で当然入出力も光信号になるため、光インターコネクトが必要である。

一方Broadcomの方は動機が違っている。同社は大規模イーサネットスイッチのベンダーでもあって、例えば2019年に発表したTomahawk 4ことBCM56990は、ワンチップで25.6Tbit/秒のスイッチング速度を誇る。25.6Tbitというのは400Gbitイーサネット×64ポート、200Gbitイーサネット×128ポート、100Gbitイーサネット×256ポートのいずれかを選択可能である。最大256ポートなので50Gbit×512ポートは不可能だ。

2022年には速度を2倍にしたTomahawk 5ことBCM78900を発表しており、800Gイーサネット×64~200Gbitイーサネット×256ポートまで対応。そして現在、速度をさらに倍にしたTomahawk 6を開発中であり、おそらく2025年頃には発表されると思われる。このスピードもたいがいなのだが、問題はこれをどうシャーシに実装するかである。

エンタープライズ向けのイーサネットスイッチの場合、トランシーバーモジュールと組み合わせて利用するのが一般的である。トランシーバーモジュールというのは、例えば安価な互換トランシーバーを多く提供しているFSの200/400/800Gイーサネットであればこんな感じだ。

実はイーサネットにもいろいろ規格があって、単に400Gイーサネットといっても山ほど、それこそIEEEで標準化された400GBASE-XXだけで10種類以上、ベンダー独自のものやIEEE以外で標準化されたものまで含めると20種類以上規格が存在する関係で、イーサネットのスイッチそのものはあくまでも電気的に400Gの信号のスイッチングができる機能に留め、個々のイーサネットの規格に合わせた光なり電気の信号の変調そのものは、トランシーバーモジュール側に留めておくことで、トランシーバーモジュールの交換で複数種類の規格に容易に対応できるようになっている。

ここまでは良いのだが、問題はスイッチチップとトランシーバーモジュールの間の配線である。400Gの場合、モジュールの規格としてはOSFP/QSFP-DD/CFP8の3種類が一般的(ほかにも独自のものがあるが割愛する)であるが、400Gbpsの電気信号なんて高速すぎて通せないので、実際には50Gbps×8での接続となる。

信号はディファレンシャルで、しかも双方向分が必要なので、1ポートのモジュールには8×2×2=32本の配線が必要になる。これが64ポートだと2048本、128ポートだと4096本もの配線となる。

それでもポート数が少ない、薄型のスイッチなら基板だけでなんとか配線ができるのだが、ポート数が増えるのにともなって厚みが出てしまう。

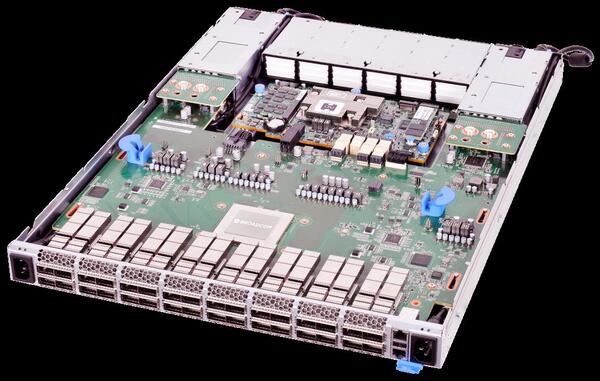

QuantaのQuantaMesh BMS T9032-IX9。1Uサイズで32ポートの400Gイーサネットポートを持つ。搭載されているスイッチはTomahawk 3

画像の出典は、Broadcomのプレスリリースより

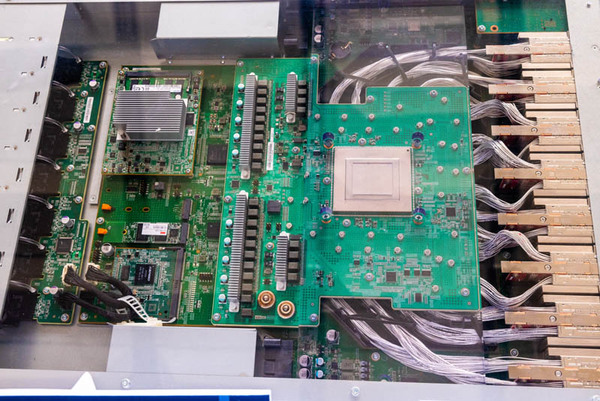

1枚の基板で配線できなくなるとどうなるか? というのが下の画像だ。

大量の配線が筐体の中を這いまわっているわけで、この先信号の高速化やポート数が増えると、さらにシャレにならないことになる。また、本来光信号のイーサネットにもかかわらずスイッチは電気信号で実装され、トランシーバーの中で光と電気信号の双方向変換をしているわけだが、この際に問題になるのが電気信号の遅さである。

先に書いたが400Gなら50G×8で送受信しているので、トランシーバー内部には50G×8と400Gを双方向変換する回路(これはGearboxと呼ばれる)が必要になるが、このGearboxの消費電力がシャレにならない。これは速度差があるほど消費電力が増える傾向にある(100G×4と400Gの変換の方が消費電力が低い)ので、できればもう少し信号速度を引き上げたい。

前置きが長くなったが今回Broadcomが発表したCPOは、こうした問題を解決するための方策である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ