ロードマップでわかる!当世プロセッサー事情 第792回

大型言語モデルに全振りしたSambaNovaのAIプロセッサーSC40L Hot Chips 2024で注目を浴びたオモシロCPU

2024年10月07日 12時00分更新

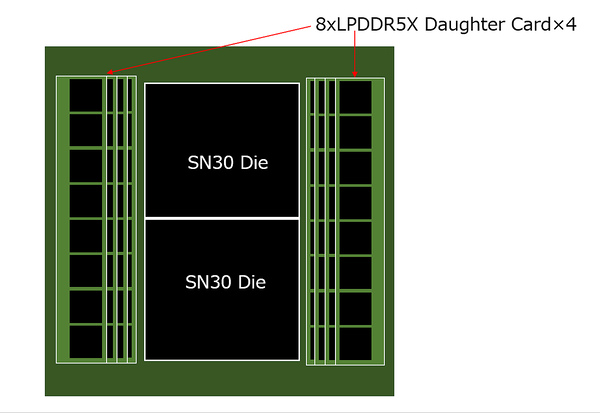

DDR5を実装したSN30

中身はLPDDR5Xをベースにしたカスタム版メモリーか?

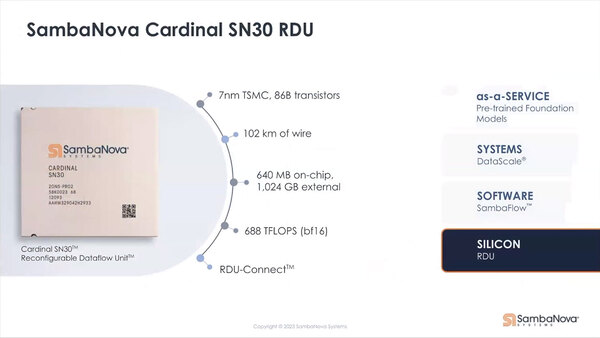

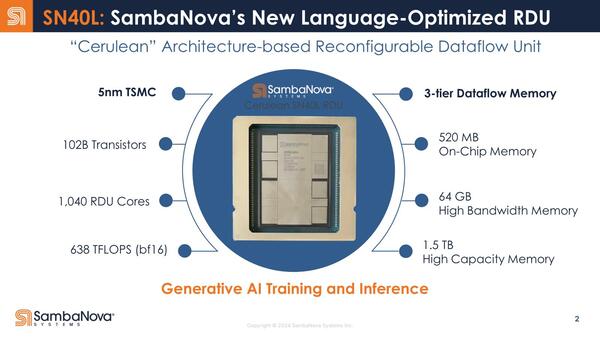

ちなみに同じ資料で、SN30のスペックが簡単に示されている。688TFlopsというのはチップ2つ分の性能と考えれば、SN20は半分の344TFlopsということになる。

SN10の320TFlopsから7.5%ほどの性能向上である。この7.5%に近いものとしては、例えば元が1.3GHz駆動でこれを1.4GHz駆動にすると7.69%ほどの性能向上で、320TFlops→344.6TFlopsという計算になる。

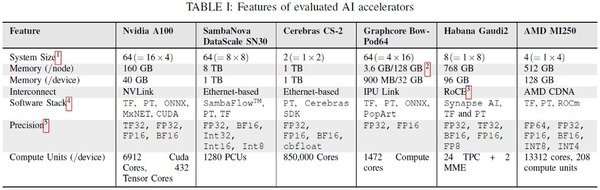

もう1つの可能性としてはPCU(Pattern Compute Unit)の数が増えることだが、アルゴンヌ国立研究所が2023年10月に発表した"A Comprehensive Performance Study of Large Language Models on Novel AI Accelerators"という論文のなかに下のような表があり、ここでSN30はPCUが1280個と明記されている。なのでSN20は640個と推察できるし、これはSN10と変わらない。

オンチップSRAMは? というと、SN10では"> 300MB on-chip memory"という表現になっており、正確なところはわからない。ただPCUとPMU(Pattern Memory Unit:SRAMである)が1:1で搭載されるのがRDUの基本構成であることを考えると、PMUの数もPCUと同じく640個で、おのおの0.5MBのSRAMを搭載して合計320MBと考えるのが妥当だろう(確証はないので、前掲の表では"?"を付けてある)。

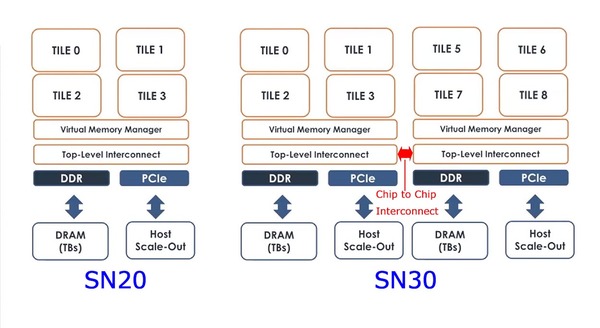

では改めてSN10とSN20の違いを説明すると、動作周波数と外部メモリーのI/F以外にもう1つ、RDU-Connectの有無ではないかと筆者は考えている。プラットフォームの説明に戻るが、640個のPMUとPCUは、160個づつに分割されており、これをタイルと呼んでいる。

SN30では合計1280 PMU/PCUなので8タイルになり、SN20では半分の4タイルであるが、SN20ではSN10と異なり、Top-Level Interconnectに外部接続用のパスが追加されたものと考えられる。そしてSN30は、このSN20を2つパッケージに搭載し、間をインターコネクトで接続したような構成ではないかと考える。チップレットというよりはMCM(Multi-Chip Package)的な接続と思われる。

さらにもう1つ謎なのが、SN30のOff-Chip DRAMである。2022年9月28日付のEETimesの記事によれば「パッケージには2つのコンピュート・チップレットと、1TBの直接接続されるDDRメモリー(HBMではない)が含まれている」とあって、これが正確だとするとパッケージの中にDDR5チップを実装していることになる。

SamsungのBlogエントリーもあるようにSambaNovaはSamsungと協業しているようなので、Samsungのラインナップで見てみるとDDR5は最大でも32Gbit品しかないため、これで1TBを実装しようとすると256チップをパッケージ内に収める必要がある。言うまでもなく不可能だ。

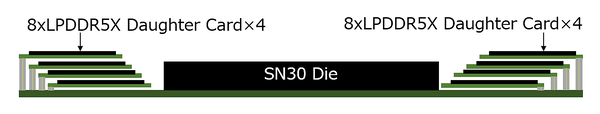

GDDR6も最大で16Gbit品なので状況はむしろ悪化する。可能性があるのはLPDDR5Xで、こちらだと128Gbit品があるため1TBは64個でいける。まだかなり多いが、256個よりは現実的である。

SN30に比べるとRDコア(つまりPCU/PMU数)はむしろ減っている。それでも性能はほとんど変わらない(bf16で688TFlops→638TFlops)のがポイント。ちなみにHBMは左上と右下のみ。右上と左下はダミー、もしくはDDR5のI/Fになっているようだ(ダミーの公算が高いが)

これも筆者の推定なのだが、SambaNovaはLPDDR5Xをベースにしたカスタム版メモリーの開発を依頼したのではないだろうか。もちろん64個を平面的に実装するのは不可能だろうが、例えば下図のような構成はあり得るだろう。

上図でいうところのドーターカードを薄くすれば現実的になるだろう(図では最下段もドーターカードにしているが、ここはパッケージ基板に直接実装でもいい)。ドーターカードを薄くすると機械的強度が気になるところだが、もともとLPDDR系は発熱が少ないので、例えば実装後に全部接着剤などで固めてしまえば(放熱には不利だが)機械的強度の確保は難しくない。というか、他の実装方法が思いつかないというのが正直なところだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ