Tenstorrentは連載706回で取り上げたばかりなのだが、先日日本支社設立の記者説明会が開催され、その際にいくつか新しい情報が公開されたので、連載706回のアップデートという形で説明したい。

TensixコアはいずれもRISC-Vと判明

まずはAIプロセッサー周りに関して。連載599回で同社のTensixコアの説明を行ったが、この際のスライドでは、Compute Engineに加えて5つのRISCコアが搭載されているという話だった。この話そのものは別に変わらないのだが、今回明らかにされたのはこのRISCコアはいずれもRISC-Vとのこと。

RISCコアとは別にArcコアも搭載され、こちらではLinuxが動くというあたり、内部の制御用コアは自前で開発した方が柔軟性が高いしコスト効率も良いのでRISC-Vを、全体を制御するコアはLinuxの移植なども必要になるので、こちらはソフトウェアがそろっているArcコアをそのまま流用するのだろう

ただしこれはJim Keller氏が携わって湧いてきたAscalonコアとはまったく異なるものであるのは間違いない。というのはTensixコアそのものは2017~2018年にはもう設計が終わった段階であり、まだKeller氏が同社に参画する以前の話だからだ。

またAscalonコアはいずれもスーパースカラー/アウトオブオーダー構成(D2などは少し怪しいが)をベースにしているのに対し、上のスライドにあるようにTensixコアに内蔵されているのはシングルイシューでおそらくインオーダーなコアなのでまったく異なる。

RISC-Vを選んだ理由は比較的簡単に推定できる。まったく独自の命令セットでは、社内でのみの利用、つまりTensixコアの内部のプログラムはTenstorrentのみが扱えるように限定したとしても、それなりに開発ツールの移植などが必要である(後述のように、この前提も怪しい)。

RISC-Vコアならこのあたりがすでに存在するので、最低限の環境はすぐそろうことになる。またインオーダーのRISC-Vコアはすでに大量に存在し、しかも無償提供されているものも多く、少なくともAIプロセッサーを自前で開発しようとしている会社にとっては、スクラッチから作るのもそう難しくはない。逆にあえて他のアーキテクチャーを選ぶ方が変だろう。

次にロードマップ。一番最初のJawbridgeは試作品であって、製品としては推論向けのGrayskullと学習向けのWormholeがすでに完成、次いでWormholeの後継であるBlackholeが現在設計中という話は連載706回で説明したが、これに続いて2024年中に投入を予定している推論向けのQuasarと学習向けのGrendelという2つの製品を開発中であることが明らかにされた。

Grendelは“Grendel and the Masters of the Universe”からだと思うが、なぜアダルト指定になっているのだろう? Quasarの方はおそらくPlanets Quasar Shield(という名前の盾)が由来だろうか? どちらもMaster of the Universeからというのは変わらないようだ

細かいスペックは上の画像に記載されているとおりで、ラフにまとめると下表になる。

| Tenstorrentが開発中のプロセッサー | ||||||

|---|---|---|---|---|---|---|

| 製品名 | プロセスルール | サイズ | 演算性能 | |||

| Black Home | 6nm | 600mm2 | 1000TFlops | |||

| Quasar | 4nm | 250mm2 | 650TFlops | |||

| Grendel | 3nm | Chiplet | 不明 | |||

Black HoleはWormhole比で3倍近い処理性能であるが、メモリー帯域は1.5倍程度でしかないので、Wormhole上で稼働していたネットワークをそのまま乗せ換えても性能がきちんと出ない可能性がある。

もっともWormholeは連載706回で説明したように、多数のチップを接続してシステムを構成するのが前提の製品であり(したがって上の画像にも“Networked ML Processor”とある)、一方Black Holeは単体動作(“Standalone ML Computer”)が前提なので、Wormholeで稼働するネットワークをそのまま乗せ換えることは考慮していないのだろう。

Quasarは推論向けではあるが、D2D(Die-to-Die)I/Fを装備しているというのは後述するチップレットビジネス向けのコンポーネントとして提供する気があるのは間違いない。ただスタンドアローンでGDDR6のI/FやPCIe I/Fも装備しており、これ1つ、あるいは2~4個のチップを乗せてPCIeカードとして出すことも考慮しているようだ。

そしてGrendelであるが、もうこちらは完全にチップレット構成であり、CPUチップレットとAIチップレット、それにメモリーI/Fや3次キャッシュのチップレットを組み合わせることが前提である。

実はこのGrendelという名称は、このチップレットを組み合わせた全体の名称ではなく、AIチップレットの名称なのかもしれない(これも後述する)。

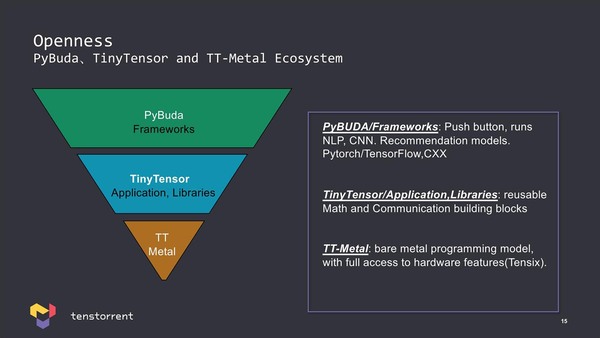

ところでAIプロセッサーを扱うためのライブラリーだが、同社は上位のフレームワークだけでなく、一番下のTensixコアをそのまま触るためのベアメタルなライブラリーも提供する、としているのが特徴である。

先にTensix内部のRISC-Vコアの話をしたが、実際にはTT-Metal経由でこのRISC-Vコアを触ることも可能なようで、そうなると自社開発のCompute Engineは仕方ないとしてもRISC-Vコアに関しては開発ツールがすでに存在するのは間違いなくメリットだろう。

PyBUDA/TinyTensorに関してはその上位のフレームワーク/APIとして提供されるとしている。それはともかく、TT-Metalを提供するということであれば当然Compute Engineの詳細も公開されないと使いようがないのだが、そうした情報がいまだに出てこないで、このあたりはNDA契約の元で開示されるのかもしれない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ