配線密度をさらに3倍に上げたFoveros

さて本題はここから。今回のIEDMでインテルは8本の講演を行なった。そのうちの1つがPaper #27.3の“Enabling Next Generation 3D Heterogeneous Integration Architectures on Intel Process”という論文である。要するにFoverosの話である。

Foverosの話は今年のHotChipsでも触れられており、この内容を連載682回でも説明しているが、いろいろ不明な部分が明らかにされた格好だ。

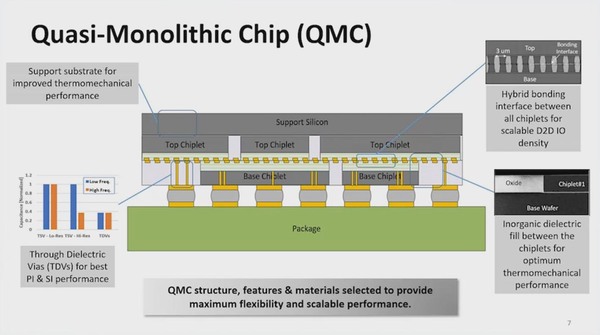

Ponte VecchioやMeteor Lakeなどがその良い例だと思うが、Chiplet(インテル用語ならタイル)を組み合わせることで、一見するとモノシリックなチップ(QMC:疑似モノシリックチップ)を作ることがすでに可能になっている。

上の画像は概念というか現実には存在しないチップであるが、Top ChipletとBase Chiplet同士は直接Hybrid Bondingで接続される。Base Chipletの中で外部に信号を出したい、あるいはTop Chipletから直接外部に信号を出したい(が、真下にBase Chipletがある)場合は、TDV(Through Dielectric Vias)を使って下に信号を引っ張ればいい。

またTop Chipletの真下にBase Chipletが存在しないケースでは、単にTDVを挟んでパッケージと接続する形になる。基本的にこの構成はFoveros Omniで実現できるという話は以前説明されたとおりだ。今回の話はこの続きとなる。

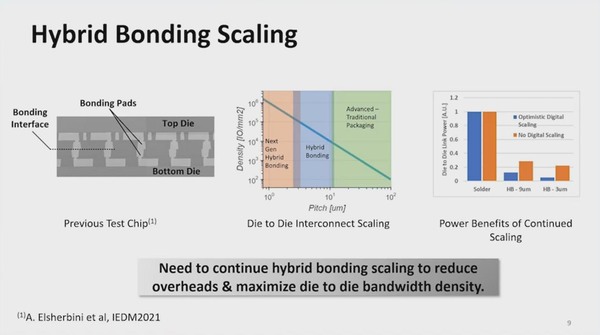

Foveros OmniはBump Pitchが25μm、つまり1mm2のサイズに40×40で1600本の配線を通せる構成になっていたが、より配線密度を引き上げる必要がある、とする。

連載682回で説明したように、Foveros Omniの次にあたるFoveros Directでは、Top ChipletとBase Chipletの間にBumpを挟まず、おそらく分子間力を利用して直接銅配線同士を接続する仕組みが使われるとしていたが、これがおそらく9μmピッチと想定されていた(正確な数字は未公表)。

これで配線密度は2.78倍、1mm2あたり1万2000本強の配線を通せる格好になるが、今後QMCがさらに広く使われるようになると、これでは足りないという話になる。今回発表されたのは、なんとピッチを3μmまで縮めたものである。

真ん中のグラフにあるように、今年のHot Chipsで公表されたものは9μmのものだったが、これの密度をさらに3倍に上げた、ということになる。

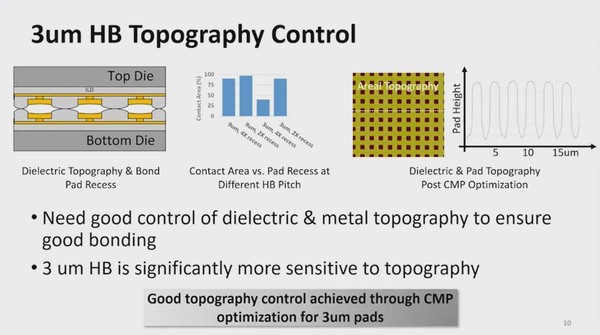

当然これでHB(Hybrid Bonding)を実現しようとすると、構造に対してより敏感になるとしているが、なにしろ接触部の面積が9分の1になるからこれは当然である。なのでCMP(Chemical-Mechanical Polish:半導体製造で、エッチングした後に不要部を取り去る際に、化学薬品などを使って削り取る工程。イメージ的にはコンパウンドを使って磨く感じになる)をうまく利用して平滑さを上げることが重要としている。

実際一番右にあるパッド(接触部)の高さの測定結果を見ると、側面がほぼ垂直に立ち上がるようになっているのがわかる。これが斜めになったりしていると接触面積が減ってしまうわけで、このあたりをうまく作り込むことが重要とする。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ