12月4日~8日にかけて、サンフランシスコでIEDM 2022(正式名称は2022 IEEE International Electron Devices Meeting)が開催された。サンフランシスコで、と書くことからわかるようにこちらはリアルイベントであるが、オンラインの形でも12月12日から内容が公開されている。

このIEDM、ISSCC(International Solid-State Circuits Conference)やVLSI Symposiumなどと並んで、主に半導体のデバイスそのものに関する重要な学会となっている。

当然ここでは多くの半導体関係企業や研究所、大学などからの発表が行なわれているわけだが、インテルも例に漏れずここで多数の発表をしている。なにしろ合計で11本の講演を行なっており、うち3つは招待講演である。今回はこのIEDMにおけるインテルの発表内容を解説したい。

ちなみに5日間ものイベントではあるが、初日はチュートリアルセッションで、合計6本のチュートリアルが開催される。チュートリアル、といってもまったくの素人ではなく、半導体にはそれなりに知識があるが、その分野には明るくないという人のためのセッションなので、初心者向けでは全然なかったりする。

翌日はShort Courseと呼ばれる、8時間半にもおよぶ「全然Shortではない」特定分野向け集中講座が2本実施される。今年で言えばShort Course 1が“High-Performance Technologies for Datacenter and Graphics to enable Zetta Scale Computing”、Course 2が“Next-Generation High-Speed Memory for AI and High Performance Compute”となっている。

3日目からがいよいよ本番で、まずPlenary講演が3本(それぞれ45分)行なわれたあと、5日目まで最大で同時8セッションが並行開催される形で実施される。そんなわけでリアルイベントに参加しても、実は全セッションに参加するのは物理的に不可能である。それもあってオフラインの形で後から全セッションの内容を確認できるのは便利である。

Foveros Directを2023年後半に出荷

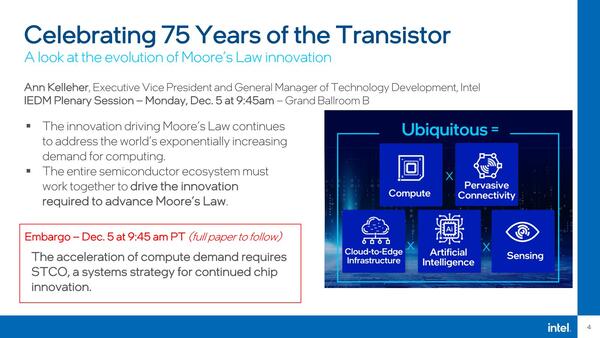

それはともかくとして、そのPlenary講演の最初に行なわれたのが、Ann Kelleher博士(EVP&GM, Technology Development)による“Celebrating 75 Years of the Transistor”という講演である。

内容はこれまでのトランジスタの発展を振り返りながら、今後もますますトランジスタの高密度化が進んでいくこと、その際の設計技法として従来のDTCO(Design-Technology Co-Optimization)からSTCO(System-Technology Co-Optimization)に切り替わりつつあること、また単にトランジスタの構造だけでなくインターコネクトや素材、メモリー素子などでも進化が必要であり、このためには新素材とか新しい露光技術、システム分割の方式、信頼性確保、製造/パッケージングやソフトウェアなど多岐に渡る分野での革新が必要で、このためには人材がさらに必要となる、と述べている。

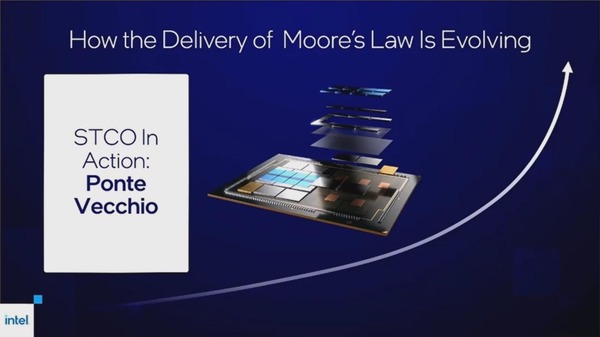

Kelleher博士の講演はわりと高いレベルの話で、あまり技術的に細かい話は出てこなかったのだが、3つほどご紹介したいスライドがある。先にSTCOという言葉が出てきたが、その実例として出てきたのがPonte Vecchioだった。

単に機能分割するだけだと、プロセス的に必ずしも合理的に分割できるとは限らない。ましてやPonte Vecchioの場合、異なるプロセスで製造したタイルを組み合わせることになるので、その設計は通常のモノリシックな製品に比べると猛烈に難しくなる。それであってもモノリシックな構成ではPonte Vecchioは構築不可能であり、これを実現できたのはSTCOのお蔭というわけだ。

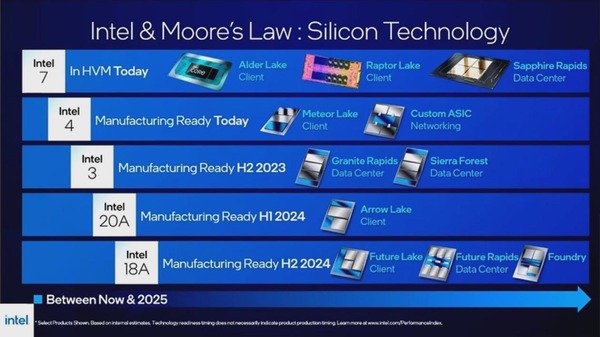

また同社のプロセスについても言及があった。一番アレなのは、すでにIntel 4がManufacturing Readyとされたことだろう。ただしHVM(High Volume Manufacturing)扱いにはなっていないあたりは、まだサンプル出荷のレベルに留まっていると判断すべきだろう。

これに続き、2023年後半にはIntel 3の量産準備が、2024年前半にはIntel 20A、後半にはIntel 18Aの量産準備が整うとされている。

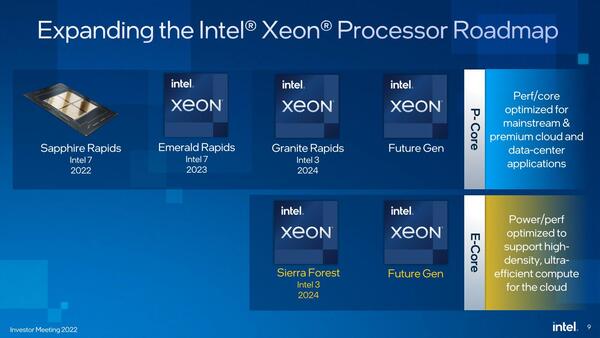

しかしこうなると、インテルのデータセンター向け製品の詰まり具合がヤバいことになる。下の画像は今年の2月に行われたInvestor Meetingのものだが、なにしろ現時点でもまだSapphire Rapidsが出荷開始されていないわけで、つまり2023年にSapphire Rapidsが出てそこから半年かそこらで今度はEmerald Rapidsが出る、という予定に切り替わるわけだ。

そして2つ前の画像のロードマップがそのまま行くのであれば、そのEmerald Rapidsの出荷と同じころにGranite RapidsとSierra Forestの生産(製品の量産は難しいだろう。おそらく検証用のシリコンの量産がスタートといったあたりだろう)し、ここで問題がなければ2024年に両製品の本格量産が始まる、というのが現時点での見通しに基づく現実的(?)なスケジュールかと思う。

しかし実績があるはずのIntel 7を使ったSapphire Rapidsがこれだけ遅れている現状、新プロセスとなるGranite Rapidsがどこまで順調に進むのか不安しか感じないのが正直なところである。

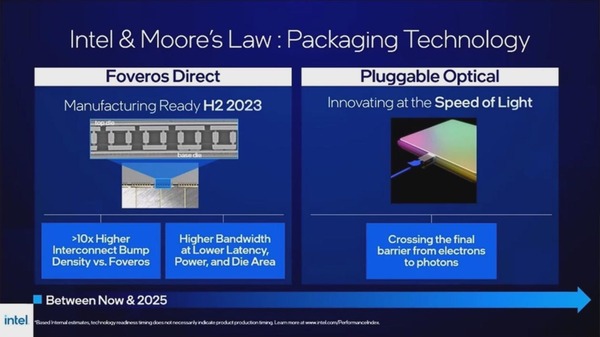

話をKelleher博士の講演に戻すと、Foveros Directを2023年後半に利用可能にすることと、2025年までの範囲でPluggable Opticsのソリューションを提供する予定であることが公開されたのが今回新しく発表された事柄となる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ