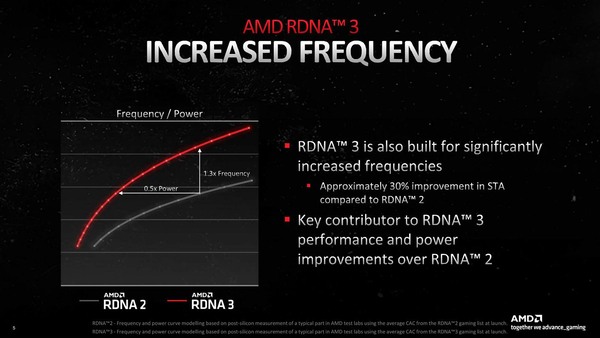

Navi 31は動作周波数がNavi 21より30%アップ

チップレット周りでもう1つ、プロセスそのものについて。Navi 31のGCDは5nmプロセスで製造されることになったが、これとNavi 21を比較したのが下の画像だ。

同一周波数なら50%消費電力削減、同一消費電力なら30%性能向上としているが、TSMCがもともと説明していた数字で言えばN7からN5に移行するとロジック密度が最大80%向上するほかに、最大15%の速度向上と30%の消費電力削減が実現できるとしていた。

もっとも製品スペックで比較すると以下のようになってしまい、平均して1割程度の向上しか見られない。

RDNA 2(Radeon RX 6950 XT) : Game 2.1GHz/Boost 2.3GHz

RDNA 3(Radeon RX 7900 XTX): Game 2.3GHz/Boost 2.5GHz

“30% improvement in STA”というからには、もう少し動作周波数の差があってもいい気がするのだが、現実問題としてはそこまでの差は見られないようだ。

ただRDNA 2とRDNA 3ではそもそも演算器の数が2倍では効かない。96CU vs 80CUながら、RDNA 3の方が実質2倍の演算器を実装していることを考えると2.4倍になる。

2.4倍の演算器をほぼ同等の消費電力でまわしながら、動作周波数が1割向上しているというのは冷静に考えればものすごい差であって、この原動力の1つがTSMCのN5の利用ということになる。

Ryzen 7000では動作周波数の高さと、これにともなう消費電力の高さが問題になったTSMCのN5だが(Ryzen 7000シリーズもECOモードで動作させると、ものすごく優秀な性能/消費電力比なのだが)、Navi 31ではうまく特性を引き出せたと言えるだろう。

1つには最大で2.5GHzと、GPUにしては高い動作周波数だが、CPUで見たらピークの半分くらいの消費電力効率の良いと言われるあたりで利用していることが挙げられるだろう。

ということでチップレット構造を説明していたらページが終わってしまった。次回はCUの中身を解説したい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ