プロセッサーパイプラインそのもののIPCは

Alder Lakeと同一

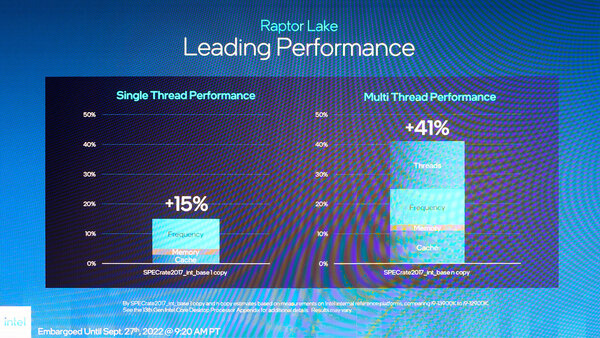

そのRaptor Lakeであるが、Intel Innovationなどでも「シングルスレッドで15%、マルチスレッドで41%の性能向上が実現」という数字が出ていた。その内訳が下の画像だ。

実はRaptor LakeもコアそのものはAlder Lakeとほとんど同じ、というかAlder LakeのGolden CoveとRaptor LakeのRaptor Coveは、事実上同一に近いらしい。

もちろんエラッターの修正などは行なわれているだろうから、完全に同一というわけではないし、後述するようにコア外部の変更はいろいろあるが、CPUパイプラインそのものの変更はZen 3→Zen 4よりもさらに少なく、事実上同じとしてみて良さそうである。

それにもかかわらず性能が伸びたのはなぜか? というと、シングルスレッドで一番大きいのが動作周波数の向上で、次がキャッシュの大容量化、最後がメモリーの高速化である。そしてマルチスレッドではスレッド動作そのものの変更が最大の性能向上要因となっている。

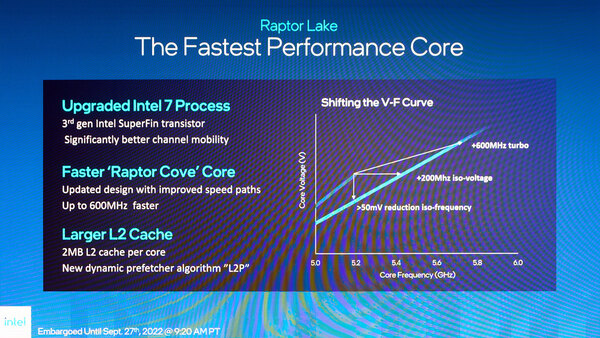

まずプロセスについて。上で書いたようにRaptor LakeではIntel 7プロセスそのものが小変更された。あくまでも「小」変更というところがミソで、実際Dan Rogers氏(Senior Director, Mobile Product Marketing)に「なにをいじったの? 構造? 材質? それともジオメトリ?」と突っ込んだものの、明確に「なにをどう変更したか」の答えはなく、その代わり「(結果として)よりチャネルの(電荷の)移動量が大幅に増えた」という返答が戻ってきた。

このIntel 7と改良型Intel 7を比較した場合、以下のようになる。

- 最大動作周波数は5.2GHz→5.8GHzで600MHz向上

- 同じ5.2GHz動作なら50mVコア電圧を下げられる

- 同じコア電圧なら200MHz動作周波数を引き上げられる

実際Alder LakeベースのCore i9-12900KとRaptor LakeベースのCore i9-13900Kを比較した場合、それぞれ1割程度の動作周波数向上が見られる(Base Frequencyだけはむしろ下がっているが)。

| 上の画像に掲載されていないオレゴン担当のプロセッサー | ||||||

|---|---|---|---|---|---|---|

| 年号 | Core i9-12900K | Core i9-13900K | ||||

| Max Turbo Frequency | 5.2GHz | 5.8GHz | ||||

| Turbo Boost Max Technology 3.0 Frequency | 5.2GHz | 5.7GHz | ||||

| Performance-core Max Turbo Frequency | 5.1GHz | 5.4GHz | ||||

| Performance-core Base Frequency | 3.2GHz | 3.0GHz | ||||

| Efficient-core Max Turbo Frequency | 3.9GHz | 4.3GHz | ||||

| Efficient-core Base Frequency | 2.4GHz | 2.2GHz | ||||

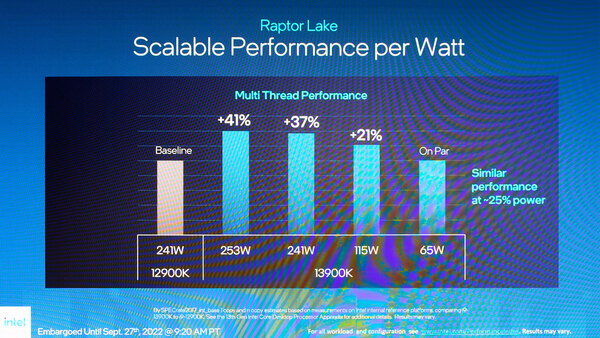

もっと興味深いのはこちらの下のスライドだ。241W駆動時のCore i9-12900Kと、65W駆動時のCore i9-13900Kは、ほぼ同等の性能になる、というものだ。

そこから50W増やして115W駆動にすると21%性能向上、176W増やして241Wにすると37%向上する、188W増やして253Wにすると41%向上するというものだが、なんというか筆者だったらこれは間違いなく65W固定で動作させたくなる。

消費電力を3.9倍まで増やしても性能が41%しか上がらない、というあたりが昨今のプロセッサーの最大の問題ではあると思うのだが、もちろん売る側としては「性能が変わらずに消費電力を176W落としました」よりも「消費電力が同じで37%性能が上がりました」の方が売りやすいわけで、性能の伸びは明白とは言え、やや複雑な心境になってしまった。

ちなみにDan Rogers氏によれば、“BIOS SettingでConfigurable TDPを設定して65W動作は可能だし、今後はよりTDPの低いSKUの投入も予定している”とのことで、筆者などにはこうした使い方のほうがありがたい気がする。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ