Slingshot-11の中核となる

ネットワークコントローラーのCassini

Slingshot-11を発表したのはKeith D. Underwood氏(Senior Distinguished Technologist, HPC&AI, HPC)だが、Underwood氏の前職はCray Inc.のSenior Principal Engineer、さらにその前はインテルでLead Architect for HPC Interconnectsの職にあり、要するにCrayは一旦HPC向けインターコネクトのハードウェアを捨てたものの、改めて開発を始めることになり、それがHPEに買収された後も続いていたのだと思われる。

ちなみにUnderwood氏がインテルからHPEに移籍したのは2019年5月なので、2012年にCrayから買収したインターコネクトのことはよく知っていたと想像できる。

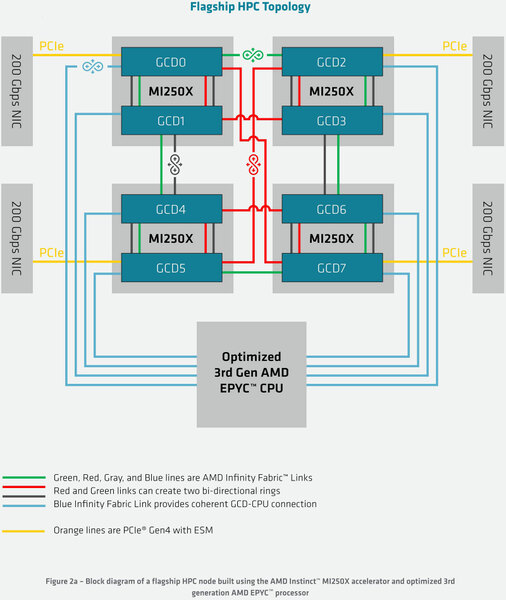

Slingshot-11が初めて全面的に利用されたのは、Frontierである(中途半端な言い方なのは、Perlmutterも途中からSlingshot-11に切り替わったため)。Frontierの基本的な構造は連載635回、正確なノードの構成は連載644回、動作周波数などのパラメーターは連載670回でそれぞれ説明したが、連載644回のこちらの図で、おのおののInstinct MI250Xから出ている200Gbps NICがSlingshot-11である。

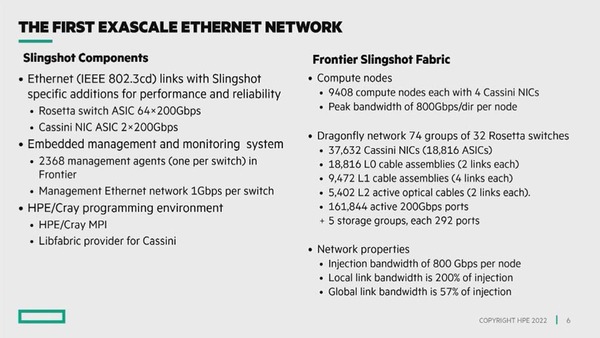

Cassini、というのがコントローラーの名前であるが、そのCassiniの簡単な説明が下の画像だ。システム全体で言えば、Rosettaベースのスイッチが全部で2368台ある計算になる。

Cassiniの概要。74グループということは、1グループにはおよそ127ノード強が含まれることになる。おそらく基本は1グループ128ノードで、1グループのみ64ノードということか? おのおののノードが32 Rosettaスイッチというあたりからもこれが想像できる

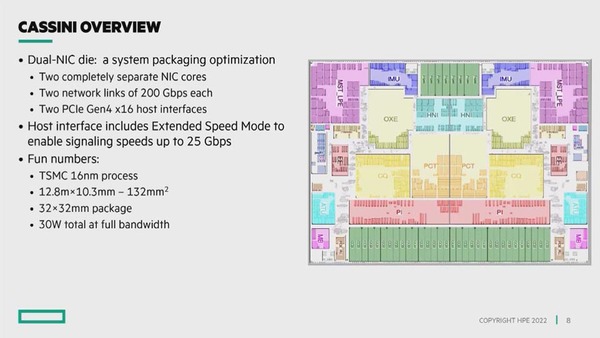

RosettaそのものはSlingshot-10の世代から変化がなく、違いはSlingshot-11のみになる。最大の違いは、Slingshot-10のConnectX-5が100Gbps×2だったのに対し、Cassiniは200Gbps×2になったことだ。またHost I/Fも2つになっている。

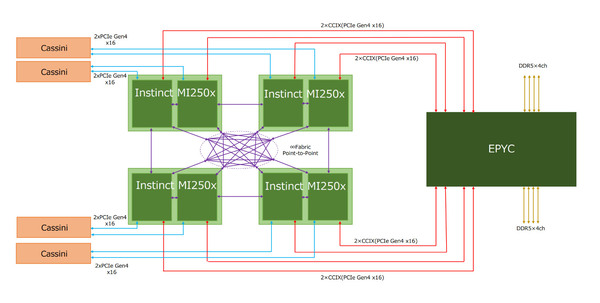

連載635回でFrontierの内部推定図を書いたが、実際には下図のような構成になっていることがわかった。またHost I/F、つまりInstinct MI250xとの接続は最大25Gbpsまで信号速度を引き上げられるとしている。接続はx16レーンなので、帯域は50GB/秒に達することになる。

ただ物理的に言えば完全に2つの200Gイーサネットを1つのダイで構成したような構造であり、言ってみればConnectX-5を2つ、1つのパッケージに収めたような構成である。

イーサネットでありながら、TSMCの16nmで132mm2という巨大なダイである。もっとも2つ分と考えれば1個66mm2なので、極端に大きいとも言いにくい。30Wの消費電力も、トータルで400Gbpsと考えると、妥当な数字に思える

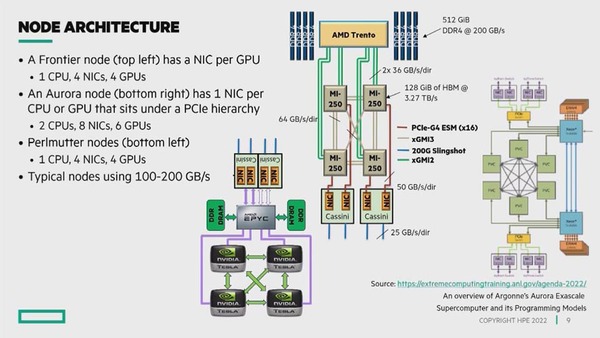

Cassiniは、FrontierとPerlmutter、さらにはAuroraにも採用されることなっている。

接続のされ方はそれぞれ異なり、以下のようになっている。

| Cassiniの接続方法 | ||||||

|---|---|---|---|---|---|---|

| Perlmutter | 1つのEPYCから2つのCassiniがPCIeで直接接続 | |||||

| Frontier | 4つのInstinct MI250Xからそれぞれ1つのCassiniがPCIeで直接接続 | |||||

| Aurora | 2つのSapphire Rapidsからそれぞれ2つのCassiniがPCIe Switch経由で接続 | |||||

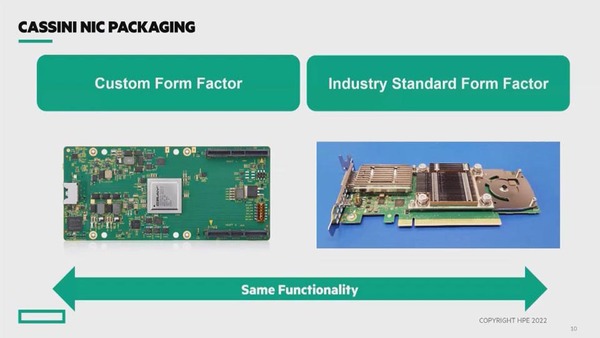

AuroraでPCIeスイッチを挟む理由は、Sapphire RapidsからはPCIe Gen5 x16が出て、これをPCIe スイッチ経由で2×PCIe Gen4 x16に変換するためであろう。またCassiniはPCIeカードとチップでの提供の2種類が用意されるとしている。

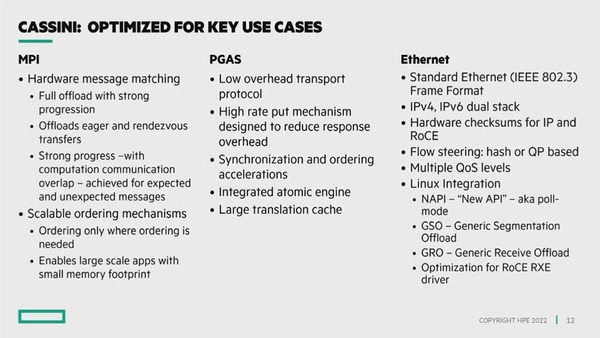

ソフトウェアから見たCassiniの特徴は下の画像のとおり。HPCでプロセッサー間通信や同期などに使われるMPIに向けたハードウェアアシスト機構やPGAS(Partitioned Global Address Space:区分化大域アドレス空間)と呼ばれる並列計算向けのアドレスモデルへの対応、さらにはイーサネットとして利用する場合のサポートなどが用意されているとする。

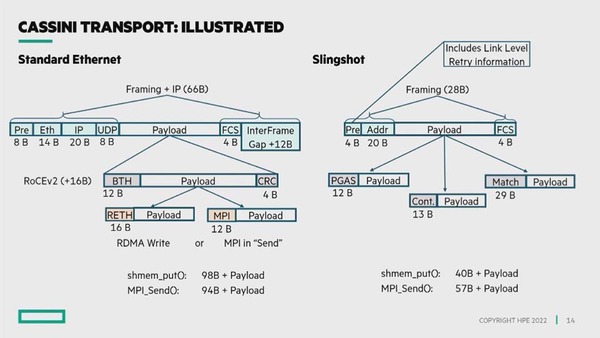

イーサネットとSlingshotの違いは下の画像がわかりやすいが、イーサネットの上にIPなどを載せると、プロトコルのオーバーヘッドが非常に大きくなるのに対し、Slingshotではそのオーバーヘッドがほぼ半減しているのがわかる。

これは特にPayload(要するに実際のデータ)が小さいときに効果的であって、トータルのパケットサイズが小さいほど通信に要する時間も、ルーティングのレイテンシーも小さく抑えられることになる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ