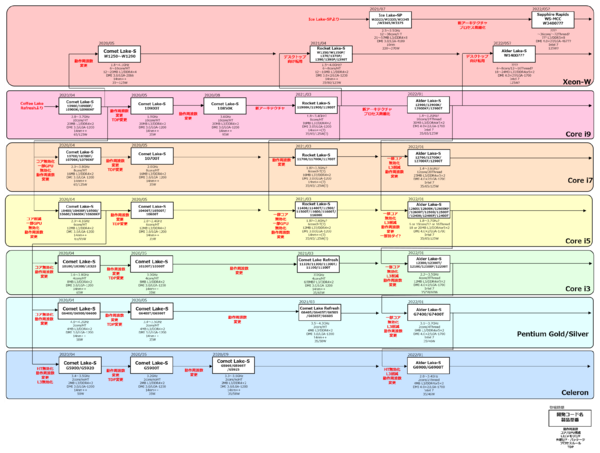

今週は連載638回の更新、というか答え合わせの回である。CES 2022におけるインテルの発表内容はこちらにまとまっており、エントリーモデルに関してはKTU氏の検証レポートもすでに掲載されているが、あらためて説明しておきたい。

Core-Xブランドはどうなるのか?

というわけでさっそくロードマップの更新であるが、上から順に説明していきたい。まずXeon-Wに関して。連載638回で、Core-Xが事実上消滅したっぽいと説明したが、このCore-Xの扱いに関して、CESの基調講演の翌日にオンラインでインテルのAaron McGavock氏(Principal Engineer, Desktop, Workstation & Channel Group)とColin Helms氏(Enthusiast Laptop Marketing Strategist)のお2人に「結局Core-Xのブランドはどうするつもりなの?」と直球の質問をぶつける機会に恵まれた。

お2方の返事は以下のとおりだ。

【McGavock氏】「まだハイエンドのデスクトップ製品は未発表であり、未発表の製品に関しての言及はできないが、いずれ詳細が公開されることになると思う。ただ、それは今ではない。そして、私が知らないところでブランドの変更があるかもしれないが、それに関するコメントは出来ない。個人的には、Extreme EditionがDesktopとMobileの両方で復活するのを見てみたいとは思うが」。

【Helms氏】「モバイルでも復活したら素晴らしいだろうねぇ。ただどうなることやら。とりあえず、ようやく素晴らしい製品(Alder Lake Mobile)を世の中に出せた」。

という、公式には肯定も否定はしない態度ではあった。ただハイエンド製品を用意しているのは間違いないところで、問題はそれのブランドということになる。

弾の方はすでにあって、それはSapphire Rapidsベースとなる。Sapphire Rapidsは以下の4つのSKUがあるとされる。

| Sapphire RapidsのSKU | ||||||

|---|---|---|---|---|---|---|

| SPR-SP XCC | 最大56コア。8ソケットまで対応 | |||||

| SPR-SP 112L | 最大56コアだが1ソケットのみ。その代わりPCIeが112レーン出るもので、HPC向けのCPU+GPU構成におけるノードコントローラー向け | |||||

| SPR-SP MCC | 最大36コア構成で8ソケットまで対応 | |||||

| SPR-MSWS MCC | 最大36コア構成ながらワークステション向け | |||||

この世代ではSapphire RapidsもMCM構成に切り替わる関係で、ダイそのものは同一でも複数のSKUを作りやすい。ハイエンドデスクトップ向けはこのSPR-MSWS(Sapphire Rapids-Main Stream WorkStation)向けをそのまま流用する形になる、と見られている。

現状聞いてる限りでは、やはりこれをCore-Xとして投入する可能性はほぼないようで、Xeon-Wブランドということになる。競合製品であるAMDのThreadripperもすでにデスクトップ向けではなくワークステーション向けになってしまっているから、ブランドという意味でもXeon-Wの方がリーズナブルなのであろう。

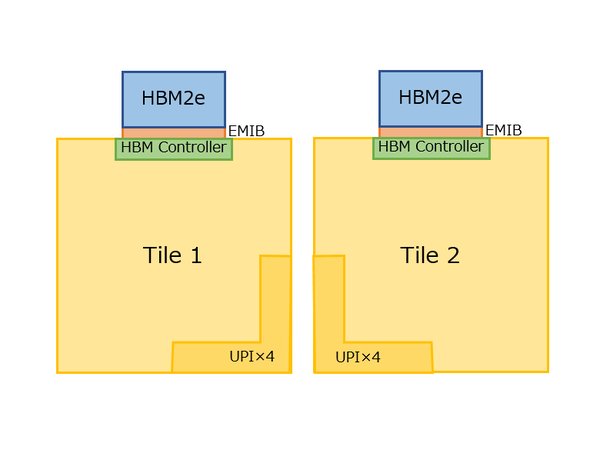

ところでそのSapphire Rapidsの構成は連載631回で説明し際にで触れたが、「ダイは1種類だが、HBM2Eのコントローラーを2ヵ所に用意する」案と「ダイが2種類」の案が考えられるとした。連載631回の時点では正解が不明だったのだが、昨年10月にLinley Fall Processor Conference 2021が開催され、直接インテルの担当者に質問を出す機会があった。結果は「2種類のダイが存在する」方式であることが確認できた。

以上のことから、Core-Xに関しては引き続きロードマップからは落としている。一方のXeon-Wの方であるが、こちらはまずサーバー向けのSapphire Rapidsがリリースされてからになりそうだ。おそらくはそれに先立ち、現在のXeon-W 1300シリーズの後継として、Alder LakeベースのXeon-W 1400シリーズが投入されるものと思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ