ロードマップでわかる!当世プロセッサー事情 第633回

Ponte VecchioとIntel Arcに関する疑問をRaja Koduri氏が回答 インテル GPUロードマップ

2021年09月20日 12時00分更新

Xe-Linkは8タイルの相互接続でしか使えず

スケールアウトにも利用できない

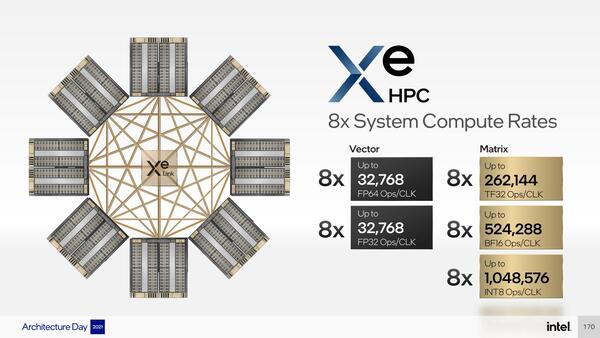

Xe-LinkはすべてのタイルがPeer-to-Peerで接続される構造になっている。これを例えばツリー構成にしたり2D/3Dメッシュにしたりする方策を取れば、より多くのタイルを接続できるし、あるいはスケールアウトの方向(つまりラック内の別のタイルグループに接続するなど)にも応用できそうではあるのだが、これに関しては「現状のXe-Linkの能力は限られている」としており、あくまで8タイルの相互接続の形でしか使えないこと、それとスケールアウトには利用できないとした。

実際アルゴンヌ国立研究所に納入予定のAuroraの場合、1枚のモジュール内の接続はXe-Linkで行なわれるが、モジュール間はHPE(旧Cray)のSlingShotで接続されることになっており、スケールアウトの接続はSlingShotのような外部インターコネクトに任せる、という返事であった。

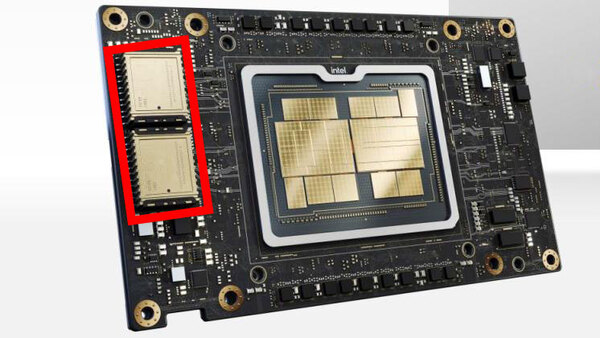

余談であるが、前回の下の画像で、筆者は赤枠で囲んだ部分をXe-Link/PCIe&CXL Bridgeと説明した。ただ、ひょっとするともう1つこのチップには用途があるのかもしれない。

PMICには大きすぎる気がするし、他のモジュールへのReTimerという可能性もあるが、Xe-Linkのままではホストと接続する方法がないので、どこかにブリッジが必要なのは事実で、このチップがブリッジではないかと筆者は考えている

実はAuroraの構成において、インテル/HPE/アルゴンヌ国立研究所のいずれもSlingShotが「どこに」接続されるのか、明示的に説明をしていない。普通に考えればCPU側のPCIeバスに接続するという形になるのだが、実はそうではない構成がある。

HPE/AMDが納入するFrontierがそれで、SlingShotがRadeon Instinct側に接続されることになっている。Frontierの場合は1つのノードがEPYC×2+Radeon Instinct×4で構成されているが、ノードあたり4つのSlingShotのEndpointが搭載されることになっている。

以上の話を念頭に、アルゴンヌ国立研究所のAuroraのインターコネクトページを見てみると、“Aurora will use Slingshot fabric connected in a Dragonfly topology with 8 fabric endpoints per node.”という文言が踊っている。つまりモジュールに8つ、SlingShotのエンドポイントが搭載されるわけで、これはどう考えてもSapphire RapidsというよりもPonte Vecchioに搭載されているとしか思えない。つまり赤枠の中のチップは、Xe-Link/SlingShot Bridgeと考えた方が良さそうな気がする。

この場合PCIe/CXLがどこから出てくるのか? という疑問は当然あるわけで、ひょっとするとBase Tile側にPCIeのI/Fが入るというのが普通の考え方だが、大穴としては赤枠の中のチップがDragonFly Endpoint兼PCIe/CXL Bridgeという可能性も残されている。このあたりは来年Auroraが導入される時期にはもう少し詳細が明らかにされることを期待したい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ