ライバルのAMDがOpteronを市場に投入

インテルはItaniumよりx64プロセッサーの開発に注力

Madisonは2004年11月に動作周波数を引き上げるとともに3次キャッシュ9MBまで拡充している(Madison-9M)。またDeerfieldの後継としてもう少し動作周波数を引き上げて最大2P構成となったFanwoodベースのItanium 2も同じく2004年11月に発表されている。

ではこれでだいぶマシになったか? といえば、むしろ状況は悪くなった。最大の理由はAMDによるOpteronの投入である。

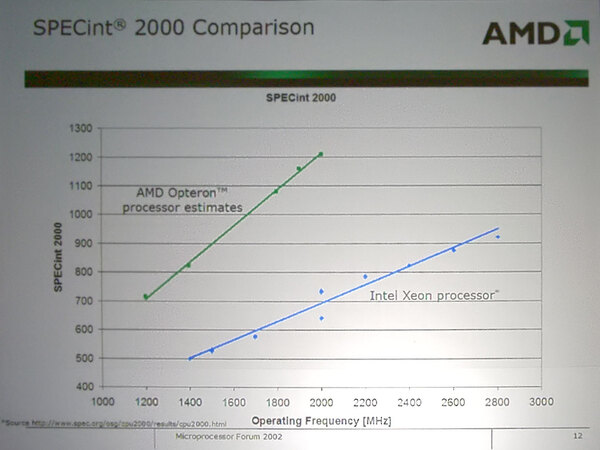

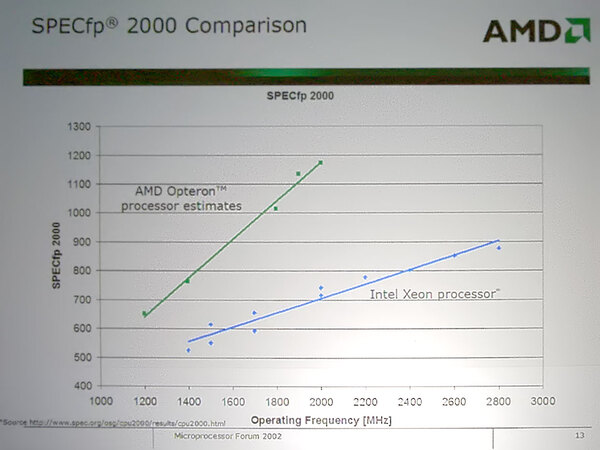

AMDは1999年のMicroProcessor Forumでx86-64を発表した。もっともこの時点ではまだ具体的な製品計画はなかったが、2001年には初代OpteronことSledgeHammerのアーキテクチャーを発表。2002年にはXeonとの性能比較を紹介した。実際のOpteronの製品出荷は2003年4月であったが、このOpteronの投入はItaniumの将来をほぼ決定的にした。

インテルは2002年当時、まだx86-64には及び腰であった。当時のインテルの考えは、x86は命令体系が複雑であり、将来性能を引き上げる際にはこの命令体系の複雑さがボトルネックになると考えていた。複雑にしたのはインテル自身だろう、という突っ込みもなくはないが、それはおいておく。

それもあって64bitに移行するにあたっては、クリーンな命令セットの方が好ましいと考えていた。64bitでItaniumを推進していた最大の理由がこれである。それもあって、クライアント向けの64bit命令は、まったく異なるもの(Itaniumとの互換性があったかどうかも不明)を考えていた。これがYamhillである。

この考え方そのものは珍しくない。最近で言えば、Armは64bitのArm命令(AArch64)を32bit(AArch32)とまったく互換性のない、かなりクリーンなものにした。現実問題として64bit Arm命令はすでに広範に普及していることを考えれば、必ずしも互換性を保つことは必要ではない、とは言える。

ただこれに反発したのがマイクロソフトである、という話は連載24回でした通りだ。この結果としてインテルは、x86-64をベースに、Opteronと互角以上に戦えるサーバー向けプロセッサーを投入する必要性が生まれた。そして、本来ならItaniumに注がれたであろう開発パワーは、x64プロセッサーの開発に注がれることになってしまった。

ここで冒頭の話に戻る。もしMercedが当初のスケジュール通り1999年に出荷されていたら、もう2003年の時点では少なからぬサーバー向けアプリケーションがItaniumで動いており、Itaniumの改良そのものももっと進んでいたはずだ。

2002年に130nmプロセスが利用可能になっていたわけで、Madisonが2002年に、次のMontecitoは2004年に出ていた可能性は高い。こうなるとOpteronに十分勝る性能を実現しており、すでに多数存在していただろうサーバー向けアプリケーションをもって確実にシェアを握っていたと思われる。もちろんそれでも長期的にはx86-64に市場は奪われたかもしれないが、少なくともずっとマシになっていただろう。

実際はMadisonの性能は、例えばSPECint_base2000だと日立のBladeSymphony(1.66GHz/9MB Itanium 2)で1502、一方2004年6月に発表されたXeon 3.6GHz+SuperMicro X6DH8/E-G2の構成で1651といったところで、ギリギリXeonに追いついていないが、これは2004年発表の製品同士の比較である。

もしMadison-9Mが2002年に出ていれば、性能比較はXeon 2.8GHzあたりになり、これを搭載したHP Proliant BL40pの性能は1202ほど。十分にx86に勝てていることがわかる。

HPがItaniumの開発を中止

インテルも開発トップが辞任

x86の64bit拡張をインテルも受け入れざるを得なくなったことで、Itaniumは急速に影が薄くなっていく。2006年7月には90nmプロセスを利用したデュアルコア構成となり、しかもマルチスレッド(SMTではなくCGMT:Coarse-Grain Multithreadingという実装である)を実装、さらに仮想化サポートなども加えたMontecitoベースのItanium 9000シリーズが発表されるが、これに先立ちIBMとDellはItanium搭載製品の販売を2005年中に中止した。

HPはItaniumの開発を中止。開発部隊はまるごとインテルに移籍となった。なによりインテルでItanium推進の旗振り役であったMike Fister氏(SVP, Enterprise Platforms Group)が2004年5月にインテルを辞任したことで、Itaniumは推進力を失うことになる。

この結果、Itanium 9000のあたりからインテルのItaniumに対するメッセージは次第に変化してきた。相変わらず性能や消費電力効率は誇るが、その対象は全世代製品(Madison)や他社のRISCベースメインフレーム(IBMのPOWER5など)であり、Xeonとの性能比較はめっきり姿を消した。

そしてXeon系列との差について「Itaniumは基本設計の時点からRASなどの高信頼性機能を組み込んでおり、コンシューマー向けのコアに後付けでRAS機能を付加したXeonとは異なる」という表現で、この時点でも残る、いわゆるRISCメインフレーム市場を本格的に攻略しにいく姿勢を示した。2007年にItanium Solution Allianceの発表会が開催されているが、この内容を見るとこうした傾向がはっきりわかる。

2007年には、このMontecitoの機能強化版としてMontvaleがItanium 9100シリーズとして投入される。動作周波数はおおむね同等ながら、FSBの動作周波数が引き上げられるとともに、DBS(Demand Base Switching)という省電力機構の搭載、さらに一部製品では2つのコアを同期して動かすことで片方のコアが故障時に直ちに代替作業を行なうLockStep機能が搭載された。

LockStepは、かつてTandemのIntegrity S2で実装された仕組みで、最近では自動車向けなどの「止まると人命に関わるシステム」などで広く使われているが、これをチップ内部で実装した形だ。

ただ、その一方で性能そのものはMontecito→Montvaleではほぼ同じであったし、DBSの搭載でシステム負荷が低い時の消費電力を減らすことで長期的にならした場合のTCO削減は実現できたものの、稼働時の消費電力そのものは同じであった。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ