初の出荷製品となるMckinleyは

Xeonより性能が悪い

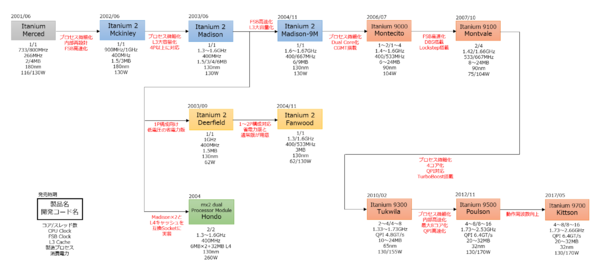

Itanium製品のロードマップを下図に示す。ここから順次説明していく。

Mercedに代わり、2002年6月に発表されたのがItanium 2ことMckinleyである。国内では発売が2002年7月にずれ込んだが、本国では6月末に発売されている。実質的にはこれがItaniumの最初の製品であるが、多少動作周波数やFSB周波数を引き上げたとはいえ、その前年にはFosterベースのXeon(WillametteのXeon版)が発表されており、こと32bitアプリケーションの性能に関してはこのFosterには敵わなかった(おおむね3分の2の動作周波数のPentium IIに同等とされたので、1GHzのItanium 2がだいたい667MHzのPentium II相当である)。

Xeonの側は、2002年2月にはさらに動作周波数を引き上げたPrestonia(NorthwoodのXeon版)を投入、さらにXeon MP向けに3次キャッシュを追加したGallatinを追加投入するなど、どんどん性能改善がなされており、この勢いに追従するのは難しかった。

なんというか、4PのXeon MPと16P構成のItanium 2が同等性能という、やや悲しい状況である。もちろんXeonにはないRAS機能や、64bitメモリーアドレス空間といったメリットはまだ確かにItaniumにはあり、こうした点を買われてシステムとしてリリースはされていた。

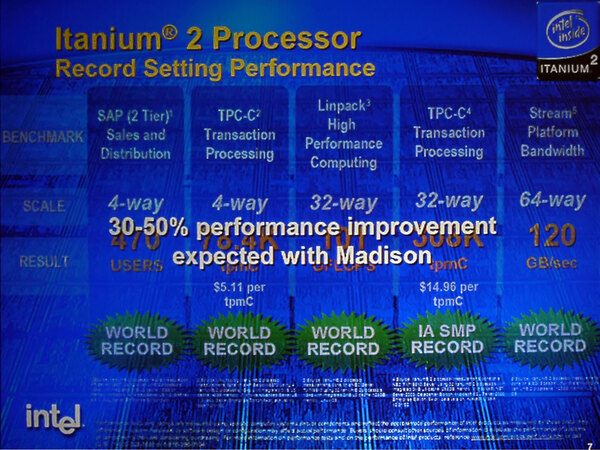

とはいえ、性能の劣勢は少しでも削りたい。そこで2003年にはプロセスを130nmに微細化し、動作周波数を引き上げるとともに2次キャッシュを最大6MBまで増やしたMadisonベースのItaniumが投入される。動作周波数もさることながら内部構造の改良もなされ、平均して30~50%の性能改善が可能と説明された。

MicroProcessor Forum 2002におけるインテルの発表より。背後のスライドのWorld RecordはMckinleyでのもので、Madisonはここからさらに30~50%の性能改善という話であった

このMadisonには、派生型としてまずDeerfieldが投入される。Deerfieldはワークステーション向けに低電圧動作としたもので、消費電力は62Wまで下がっている。

もともとHPなどはMickinleyをベースに、なかば無理やりItanium 2ベースのワークステーションを開発していたという話は連載540回でも少し触れたが、130WのCPUをデュアル構成でワークステーション筐体にぶっこむというのは、当時としては電源供給と放熱の両面でチャレンジであり、そうしたニーズに向けたのがDeerfieldというわけだ。

2004年に投入されたHondoは、インテルの製品ではない。これはHPが開発した独自プロセッサーで、2つのMadisonと32MB 4次キャッシュ(これはPentium II/IIIなどと同じようにSRAMチップを実装する形で実現された)を、既存のMadisonのソケットに装着できるようにするモジュールだ。

発表そのものは2003年2月に行なわれたが、出荷は2004年に入ってからとなった。ちなみにこんなものを開発したのはもちろんHPだけであり、対応するのもHPのSX1000というチップセットのみである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ