HP独自のZX1チップセットを採用した

HP zx2000/zx6000シリーズ

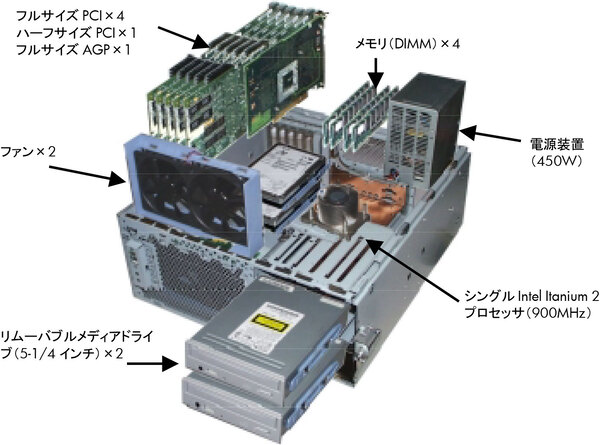

HP i2000の後継として、今度は900MHz動作のMckinleyを搭載した製品が2002年に投入されたHP zx2000/zx6000シリーズで、のちにMadison/Deerfieldを搭載したモデルも追加されている。

画像の出典は、HP zx2000/zx6000のカタログ

こちらの特徴は、HP独自のZX1チップセットを採用したことだ。まだ拡張バスはAGPおよびPCI/PCI-X対応であるが、メモリーはDDR SDRAMに対応。発表当時はまだ1GBまでの容量のDIMMしか存在していなかったので最大メモリー容量は4GBとやや減ったが、2GB DIMMが出てきたらこれを利用して最大8GBになるとされた。

ところでこのZX1チップセット、実はPA-RISCとItaniumの両対応になっており、実際2004年登場したHP 9000 rp3410(PA-8800×1)/rp3440(PA-8800 or PA-8900×1~2)はこのZX1チップセットを利用して構築されている。

なので技術的にはItaniumを搭載したHP 9000シリーズがこの時点で登場しても良いはずなのだが、HP 9000を名乗るItaniumマシンが登場するのはもっと後になる。

実を言えば、HP 9000 N-Classが最初のHP 9000系のItanium搭載製品となる予定だった。このN-Classに属するHP 9000 N4000そのものは1999年に投入されたが、当初は64bit版のPA-RISC 8500/8600/8700を1~8 CPU搭載するという構成であり、これに続いて最大2 CPUのItaniumを搭載するバージョンが追加されるはずだった。

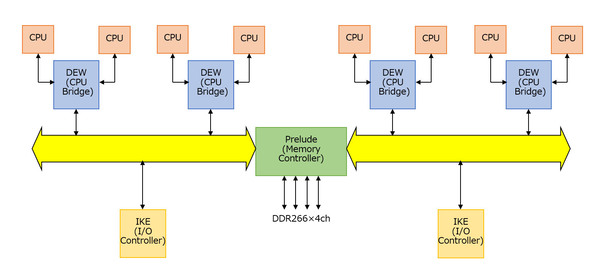

そもそもN4000に採用されていたStretchというチップセットそのものはItanium Busに対応していた。このStretchはちょっと複雑な構成で、概略は下図のようになる。

Preludeというのが中核となるメモリーコントローラー兼システムバスコントローラーで、4本のDDR-266メモリーコントローラーと2本のItanium Bus(各々133MHz/64bitで2.1GB/秒)を出す。

CPU自身はRunway BusというPA-RISCの独自Busを利用していたので、間にDEWと呼ばれるCPU Bridgeを挟み、これでRunway BusとItanium Busの相互変換を行なっていた。

ただプロトコル的にはこれでいいとしても、各々のDEWとCPUの間の帯域もやはり2.1GB/秒なので、明らかに帯域が足りてない気はするが、それはおいておく。

一方I/Oは、やはりItanium BusにIKEというI/Oコントローラーがぶら下がるが、このIKEからは266MB/sの帯域を持つI/Oリンクが12本出て、その先にElroy PCI Bridgeというブリッジチップを噛ますことでPCIなりPCI-Xが出るという構成になっている。

こういう構成であるから、Itaniumを使う場合はDEWを全部取り払い、直接Itaniumに接続するだけでいいはずである。最大2Pということなので、1つのPreludeから出る2本のItanium Busに、それぞれ1つのItaniumとIKEがぶら下がる構造を想定したと思われる。

「思われる」というのは、このItanium版のHP 9000 N4000は結局出荷されなかったためだ。理由は定かではない(なにしろ公式には一切発表がない)が、HP 9000対応ソフトウェアのItaniumへの移行準備が整わなかったとかそんな理由な気がする。そんなわけでItanium対応を名乗るHP 9000シリーズは、いきなりハイエンドのSuperdomeとなった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ