インテルの7nmとTSMCの5nmを使う

HPC向けGPU「Ponte Vecchio」

Ponte Vecchioの詳細は連載569回で説明したが、インテルの7nmプロセスを前提に作られたお化けチップである。

このインテルの7nmというのは、ジオメトリー的に言えばTSMCの5nmに相当しており、一方TSMCの6nm(N6)というのは連載553回で説明したが、N7と互換性を持ちつつ、一部をEUV化したプロセスである。これはインテルで言えば、10nmプロセスに近い(10+nmというより10++nmあたりだろうか)。

したがって、仮にPonte Vecchioを6nmで作った場合、下の画像のサイズではチップが収まらないと考えられる。

And..they let me hold peta ops in my palm(almost:)! pic.twitter.com/8kG7cv774M

— Raja Koduri (@Rajaontheedge) June 25, 2020

すでにTSMCは2019年後半からN5のRisk Production(リスクありの先行生産)を開始しており、今年6月16日に行なわれた2020年第2四半期のEarnings Call(投資家向けの収支報告)でCEOのC.C. Wei氏は以下のように述べている。

「N5はすでに量産を開始しており、歩留まりも非常に良く、またEUV装置のパフォーマンスと生産性も良好である。我々は今年後半にN5の売上が強力に伸びていくだろうと考えている。COVID-19の影響で、N5の立ち上げは若干遅れたが、今年のウェハー全体の売上のなかでN5は8%程を占めると考えている」

仮にインテルがN5を使ってPonte Vecchioを製造するとすれば、Koduri氏が初期のエンジニアリングサンプルを手にして評価していても不思議ではない。もちろんN5の最初の顧客はAppleであり、インテルがPonte Vecchioの本格量産を始めるのは2021年に入ってからかもしれないが、Auroraの納入にはなんとか間に合いそうである。

ではN6の18万枚のウェハーでなにを作るか? であるが、おそらくは10nm世代のCPUになると思われる。その10nm世代の話を次にしたい。

10nmはTiger LakeとIce Lake-SPを年内に投入

来年はAlder LakeとSapphire Rapidsを投入

再びBob Swan CEOの言明に戻ると、現在のIce Lakeに続き、まずクライアント向けにTiger Lakeが投入され、次いで年末にはIce LakeベースのXeon Scalable(つまりIce Lake-SP)が投入される。そして2021年後半には、クライアント向けにAlder Lake、サーバー向けにSapphire Rapidsがそれぞれ投入される予定だと説明している。

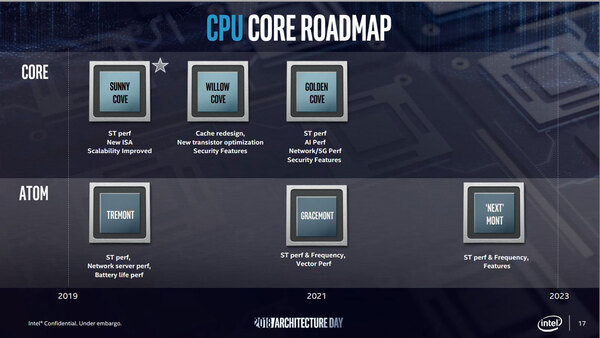

まずTiger Lakeであるが、GPUは連載569回の冒頭で紹介した通り第1世代のXeを搭載しており、一方CPUは連載511回に出てきたWillow Coveがベースになっていると思われる。

このWillow Coveは大きくは性能の改善はない(それは次のGolden Coveで行なわれる)模様だが、こちらはインテルの10nm++がターゲットと思われる。

インテルの10nm++も、なにしろ元の10nm+が、少し動作周波数を引き上げると急に消費電力が増えてしまうものだから、あまり大きく性能を引き上げるのは無理で、やはりモバイル向けのみということになる。

このTiger Lakeと対になる形で投入されるデスクトップ向けは、現在のComet Lakeのリフレッシュ版である(つまり14nm++を使う)Rocket Lakeとなる模様だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ