Zen 4は5nmプロセスと明言

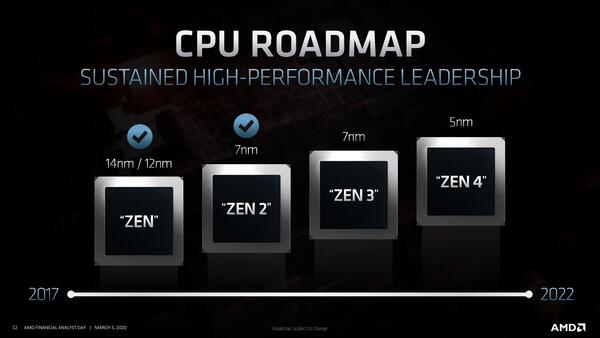

次いでCTOのMark Papermaster氏より、テクノロジー・ロードマップの開示があった。まずは2019年の振り返っての話なので割愛するとして、CPUロードマップがこちら。

CPUロードマップ。ちなみに2018年4月、(Corporate Fellowの)Michael T Clark氏がZen 5の設計をスタートしていることを明らかにしている。こちらは2023年の投入というあたりだろうか?

ここで「あれ?」と思われた方も多いと思う。以前のロードマップ(例えばこれ)と比較すると、2つの違いがある。

- Zen 3が7nm+から7nmになった

- Zen 4が5nmと明確に示された

まずZen 3について。最後の最後の質疑応答でこの件についてPapermaster氏が説明したのは、「当初と異なりTSMCが7nmで複数のオプション(N7/N7P/N7+/N6)を提供するようになったため、わかりにくいので7nmとまとめた」という話であって、Zen 2と同じプロセスを使うという意味ではない。詳細は下表のとおりで、広義にはこの4つのすべてが7nmプロセスに該当する。

| TSMCが製造する7nmのオプション | ||||||

|---|---|---|---|---|---|---|

| N7 | Zen 2やNAVIの製造に使われている、TSMCの最初の7nmプロセス。ArF液浸+マルチパターニング | |||||

| N7P | N7の後追いで追加された、N7の若干の改良型。N7とはプロセス互換性があり、N7の設計がそのまま移行可能。AppleのA13やQualcomm Snapdragon 865、MediaTekのDimensity 1000Lなどで採用された。やはりArF液浸+マルチパターニング | |||||

| N7+ | N7の製造プロセスの一部をEUV露光に切り替えたもの(全部ではない)。N7と設計の互換性がないので、N7からそのままの移行はできない。HiSiliconのKirin 990 5Gで採用されている。 | |||||

| N6 | N7の一部をEUV化したという意味ではN7+に近いが、N7+との最大の違いはN7と設計の互換性があること。N7あるいはN7Pを利用していたデザインはそのままN6に移行可能とされる。発表は昨年4月16日であり、TSMCによれば今年第1四半期からリスク・プロダクション(リスクを背負っての先行生産)を開始予定である | |||||

この状況をかんがみて、AMDでは「7nmプロセスを使う」という表現に改めたのだそうで、N7をそのまま使い続けるという意味ではないとのこと。

もっと言えば、そもそも従来までのロードマップでも、“7nm+”というのは「より進化した7nmプロセス」という意味であって、TSMCのN7+を使うという意味ではないとしている。

そのうえで、Zen 3や(この後出てくる)Navi 2Xに関して言えば、「ベースライン(つまりZen 2で利用されたTSMCのN7)を改良し、より性能の高いプロセスを使う」としている。逆に言えばN7Pを使うのかN7+を使うのかは、現時点では明確にはされていない。

ちなみにTSMCによれば、N6はN7+と比較して18%ロジック密度を上げられるとしており、その意味ではN7→N7P→N6、あるいはN7→N6というパスが王道ではあるのだが、N7+は2018年からリスク・プロダクションをスタートしており、昨年量産をスタート、すでに製品出荷も始まっているという意味では確実さがある。

設計時期から考えると、すでにZen 3は物理設計が終わってプレ・プロダクションにかかっていないといけないので、筆者はこれまでも書いてきたようにZen 3はN7+を利用しての製造になると考えている。

そしてZen 4であるが、2022年までに投入で、しかも5nmプロセスでの製造と明確化されたのが一応の相違点である。5nmの利用は既定路線であるが、この調子でいくとほぼ毎年新製品を投入というパイプラインがきちんと示されたことになる。

余談だが、プロセスについては下のスライドも示された。もうなにを言わんやという感じである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ