Predicationで半自動ベクトル化も可能

さらに独自の4オペランドFMAを実装

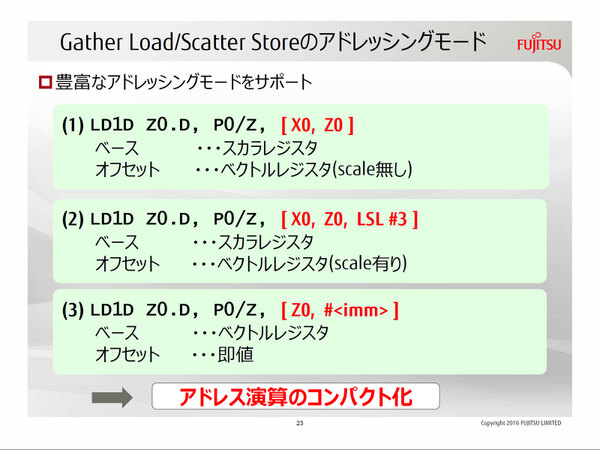

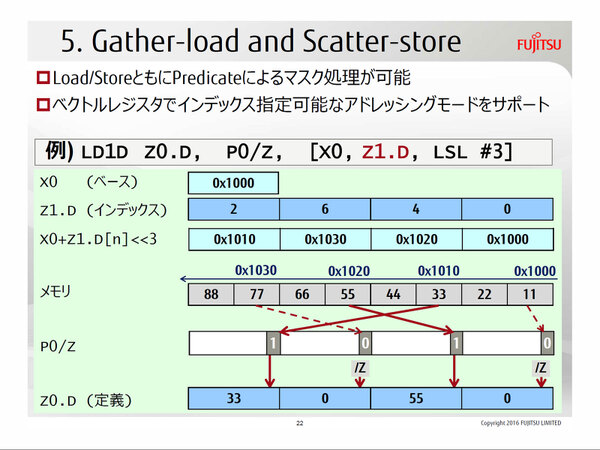

Predicationは、Load/Storeの際にも利用できる。Load/Store命令の際に、データを並べ替えながらのロードが可能(インデックスレジスターで指定)だが、これにPredicationを加えて「そもそもLoad/Storeをする/しない」の制御も可能になっている。このPredication付きロードは複数のモードがサポートされている。

ややわかりにくいが、これはZ0.Dというレジスターに、X0というアドレスから始まるメモリーの値をロードする処理で、ただし並び順をZ1.Dというインデックスでして、さらにP0/zのPredicationでロードする/しないを設定している

こうしたPredicationの指定そのものは珍しくないというか、SIMD演算では似たものはいくつかあるが、通常は個々の命令に対する拡張として実装されているのに対し、A64FXではベクトルレジスターに対する操作の一般的な手法としてPredicationが用意されているのが大きな違いである。

もっともこれは(プロセッサー内部の処理からすると)面倒な作業になるわけで、専用処理ユニットとパイプラインが追加されたのも無理ないところである。

実際、ここまでの細かな操作がサポートされていないSPARC64 XIfxには、Predicationユニットが搭載されていない。

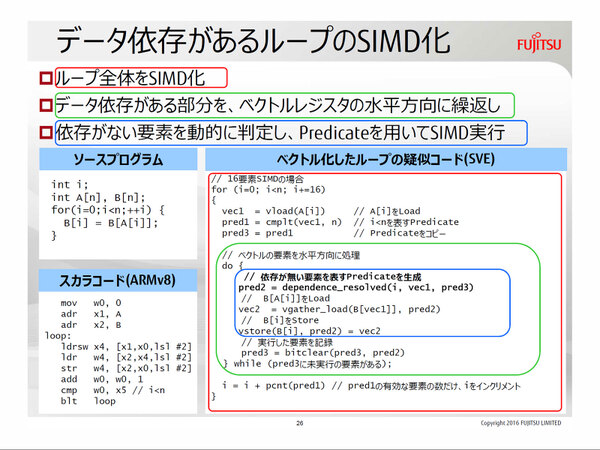

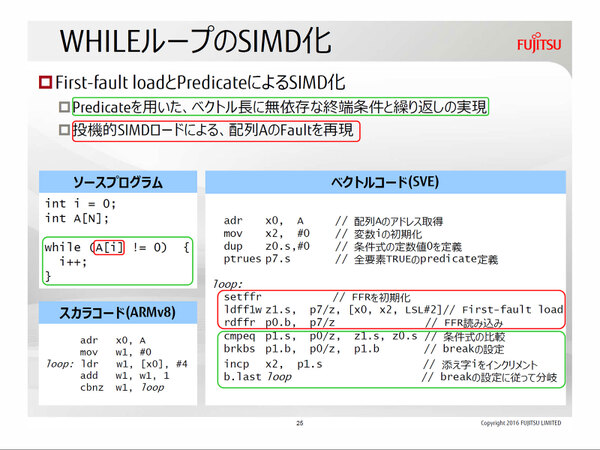

そしてPredicationと先のFirst-fault loadを組み合わせると、とてもベクトル化できそうにないコードですら、SVEでぶん回せることになる。

これはわかりにくいが、下の4命令で16要素まとめて判別している。また左のスカラーコードは、A[N]が十分大きければいずれはページフォルトを起こすはずで、その振る舞いはFirst-fault loadで再現できることになる

A[N]はintなので32bitとすれば16倍、もしこれをINT8で実装したら64倍の速度でwhileループを回せるわけだ。さらには、Predicationを使っての半自動ベクトル化も可能としている。

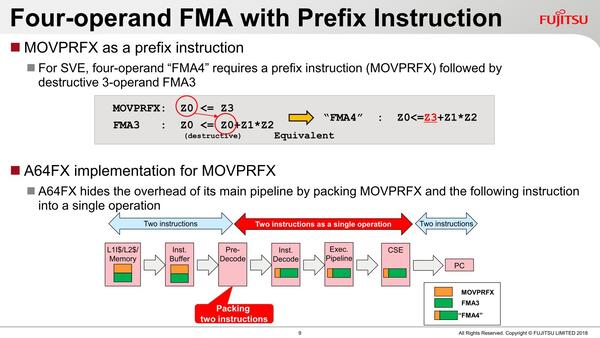

SVEに絡んだ独自の実装が、4オペランドFMAである。D=A×B+Cという一般的なFMA(Fused Multiply-Add)処理の場合、A/B/C/Dの4つのオペランドが必要になる。ただARM v8ではこの4オペランド命令をサポートしていない。

そこで、通常は上のソースにあるように2命令での処理になるわけだが、A64FXではこれを内部的に処理して、1つのFMA4命令としてハンドリングすることになる。これにより、フロントエンドでは2命令として認識されるものの、バックエンドでは1命令で処理されることになり、実質的な性能向上につながるわけだ。

消費電力を下げるために

デコードと実行ユニットを制限できる

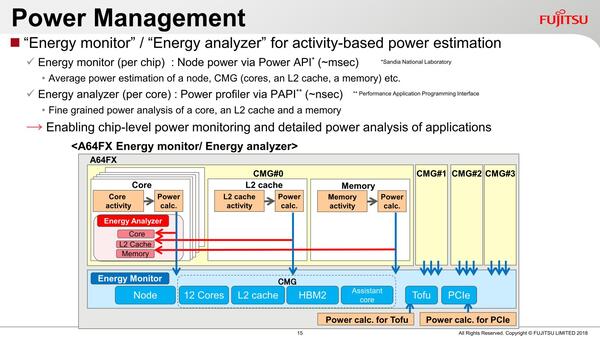

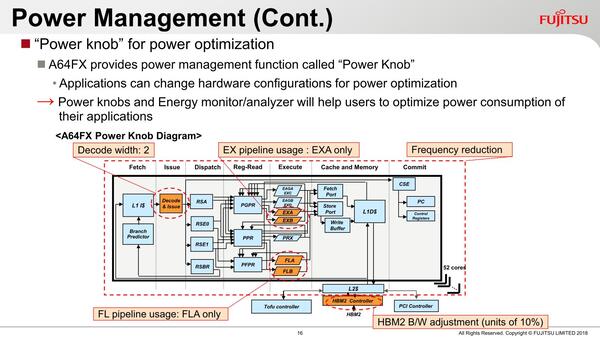

性能向上の一方で、省電力の仕組みもやや独特である。チップ単位のEnergy monitorと、コア単位のEnergy analyzerを併用し、細かく消費電力を監視しながら電圧/動作周波数を制御するというあたりまでは一般的であるが、Power knobの実装はあまり見かけたことがない。

要するに、デコードを絞るとともに、利用する実行ユニットも制限することで消費電力を下げるという仕組みである。最小に絞ると、デコードは2命令/サイクルになるし、EXB/FLBのユニットは休止になるため、実質5命令のスーパースカラー/アウト・オブ・オーダー構成になる。

ついでにHBM2のバンド幅も10%単位で絞ることが可能になる(もちろん動作周波数も下げられる)仕組みだ。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ