より高速なRISCプロセッサーの開発を開始

1985年、もともとのIBM 801開発チームが再び集結し、より高速なRISCプロセッサーの開発を決める。“AMERICA architecture”なる開発コード名が付いたこのプロセッサー、初期デザインはヨークタウンで行なわれ、1986年にデザインをAES IBUに提示。AES IBUはこれを受け入れ、ただちにAMERICA architectureベースのマシン開発をスタートする。

RT PC Workstationの後継がなかった理由の1つはこれである。そのAMERICA architecture、基本的な考え方はIPCの向上である。IBM 801では1命令/サイクルが目標であったが、スーパースカラーのような実装をすることで、1命令/サイクル以上の性能を実現可能という研究が当時すでに行なわれており、これを実装することが目標とされた。

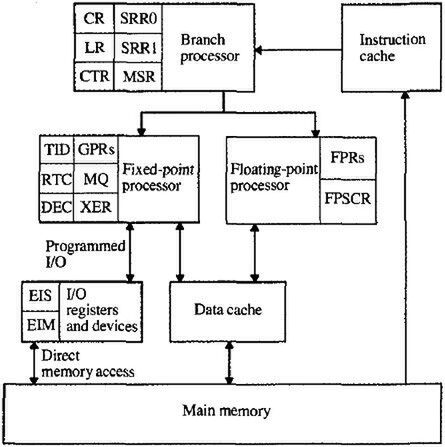

実際の実装はなかなかおもしろいものである。まず最初の特徴であるが、内部は大きく3つに分けられている。Branch Processor、Fixed-point Processor、Floating-point Processorである。

AMERICA architectureでのCPU概念図。それぞれのプロセッサーの脇の小さなものは、レジスターの管理場所である。例えばCR(Counter Register)やMSR(Machine State Register)などはBranch Processorの管理下にあるわけだ

画像の出典は、IBM RISC System/6000 processor architecture

最近のx86の実装で言えば、Branch Processorがいわゆる命令パイプラインのフロントエンドにあたるインオーダーで実行される部分である。ここは命令フェッチとデコードを行なうほか、割り込みの管理なども行なう。

また関数の呼び出しに向けたリンクレジスター(x86の実装で言えば、Call専用のスタックに相当するもの)もここで管理している。分岐命令そのものも、もちろんここで管理される。IBM 801やROMPで搭載されたディレイスロットに相当する実装や、簡単ながら分岐予測の機能も搭載された。

これに対してFixed-point ProcessorとFloating-point ProcessorはそれぞれALU/FPUにあたるものである。まだロード/ストアにあたる専用ユニットはなく、これはFixed-point Processor/Floating-point Processorからそれぞれデータキャッシュへのアクセスする形になっていた。加えて、そのFloating-point Processingの性能を大幅に強化するというのが2つ目の特徴である。

初期のデザインでは、1サイクルで64bitのMAC(Multiply-and-Add:乗加算)を可能にする予定だった。さすがにこれは実装の難易度が上がりすぎるため、実現したのはだいぶ後のモデルになる。命令セットはROMPの縮小RISC命令風から逆戻りし、IBM 801をもう少し拡張したようなフォーマット(実際4オペランド命令なども存在する)に発展した。

ちなみにアドレッシングは、ROMPのさらに上を行く52bitの仮想アドレス(セグメントIDがROMPの12bitから、AMERICA architectureでは24bitに増強された)となっているほかは大きな違いはない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ