FD-SOIより低コストで作れる

PD-SOI

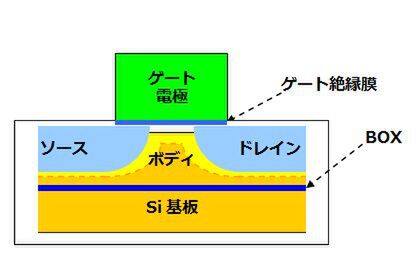

FD-SOIを使って製造された製品はあまりない。では世間に出ているSOIはなにかというと、PD-SOI(Partially Depleted SOI:部分空乏型SOI)と呼ばれるものである。これは、FD-SOIと同じくウェハーはBOXを含む3層構造なのは同じだが、BOXの上のシリコン層の厚みがずっと大きいのが特徴だ。

PD-SOIの仕組み

こうなると、ソースやドレインの周囲に空乏層が発生してしまうため、FD-SOIに比べると部分的に浮遊容量が構成されてしまう。厄介なのは、BOX層がある関係でその特性がやや変則的になることで、そのため浮遊容量を逃がす仕組みが別途必要になる。

また、先ほどは書かなかったがFD-SOIは原理的にジャンクション・リーク電流を減らす効果があり、さらにサブスレッショルド・・リーク電流も減らせるため、通常のシリコン基板(SOIと区別するため、一般にバルクと呼ぶ)と比較すると以下の効果があるとされる。

- 同じ電圧ならリーク電流全体を1/10にできる

- 同じリーク電流なら、電圧を0.1V下げられる

しかし、PD-SOIはBOX層の上に余分なシリコン層がある関係で、このあたりはほとんどバルクと変わりがないとされる。

では、メリットがなにもないか、というとそうでもなく、BOX層を入れることでPN接合の寄生容量がバルクよりも減る関係で、トランジスタの動作速度は向上するし、BOX層があることのメリット(宇宙線などの影響によるエラーに強い、動作環境温度が高くても平気など)はそのまま継承される。

一方、FD-SOIに比べると大きなメリットはウェハーのコストが安いことだ。PD-SOI向けのウェハーはバルクの数割増しといったところで、数倍のFD-SOI用に比べてはるかに安い。PD-SOI向けの厚膜SOI基板は、FD-SOIに比べると余分な工程が減っており、これが価格差の大きな要因となっている。

また、特にシリコン層の厚みが大きいためプロセス側で適当にそろえられるというメリットもある。そのうえ製造工程においても、PD-SOIのプロセスはバルク向けのプロセスとほぼ同じでいい。FD-SOIはなにしろシリコン膜が薄いので、バルクと同じやり方だとうまくいかないので、この点もPD-SOIのメリットとされる。

以上のことから、IBMは当初PD-SOIをベースに実用化、これを導入したAMDや、そのAMDのファンダリーを買収したGLOBALFOUNDRIESなどはずっとPD-SOIをベースにしてきたわけだ。ただ特性という意味ではPD-SOIのメリットはバルクと比べてそう大きくなく、コストパフォーマンスで同等というあたりを狙う技術であり、FD-SOIとは比較にならない。

FinFETとの相性が抜群なため

FD-SOIが見直される時が来た

さてそのSOIの今後はどうなるであろうか。GLOBALFOUNDRIESは32nm世代まではPD-SOIのプロセスを提供してきたが、現状28nm世代以降はバルクのみとなっている。ただ冒頭で書いたとおり、STMicroelectronicsは28nmおよび20nm向けのFD-SOIの技術をGLOBALFOUNDRIESに提供しており(関連リンク)、もし適切なニーズがあればFD-SOIが出てきても不思議ではない。

もう少しグローバルに語れば、インテルをはじめTSMCやGLOBALFOUNDRISのFinFETプロセスは、いずれもバルクをベースにしているが、本来はFinFETをベースにした方が効率が高くなる。加えて、こうした先端プロセスはすでに加工コストが高騰しており、今さらウェハーの値段が2~3倍になったとしてもすでに大した問題ではないところに来ている。

| ウェハー1枚あたりのコスト | |

|---|---|

| 40nmバルク(TSMCなど) | 30万円/枚 |

| 28nmHKMG(TSMC) | 60~70万円/枚 |

| 22nmHKMG+FinFET(インテル) | 100万円超/枚 |

| 16/14nmHKMG+FinFET(TSMC、GLOBALFOUNDRIES) | 120~130万円/枚 |

| 14nmHKMG+FinFET(インテル) | 150万円/枚(それ以上という説もある) |

昨今のウェハー1枚あたりのコストは、いずれも推定ながら上記のようになっている。なぜこんなに高騰するかといえば、HKMGやFinFETの構築に余分な作業が必要だからだ。

しかもこの作業というのはひたすら露光→化学機械研磨(CMP)の繰り返しになり、その露光が最近はシングルパターニングやダブルパターニングで済まず、トリプルだのクアッドだの複数回の露光と研磨を重ねてやっと目的の構造になるという騒ぎになっており、この手間が恐ろしく多いためだ。

したがって、露光がなんとかなれば原理的にはもう少しコストが下がるのだろうが、今のところそれがなんとかなるめどが立ってないので、価格は上がる一方である。この結果として、もうウェハーコストが多少上がったくらいはどうということはない、というレベルになっている。

またFD-SOIにしてもPD-SOIにしても放熱に弱いという話があるわけだが、その熱に弱いはずの32nm SOIプロセスを使ったAMDの「FX-9590」は220WのTDPで動作している。これは極端にしても、100WクラスのTDP製品はすでに無理なく作れているので、現状それほど熱が支障になるわけではない。

むしろ昨今のCPUが低消費電力化を進めていることを考えると、FD-SOIは非常に理想的とすら言える。先にも書いたとおりFinFETはFD-SOIと非常に相性が良いわけで、主要なファウンダリーがFinFETに移行しようとしている現状を鑑みると、次世代以降でさらにプロセスを微細化するならば、FD-SOIは有力な技法になりえるだろう。

実のところ、インテルは10nm世代まではバルクで行くのはほぼ確定である。仮にその先があるとすると、しれっとFD-SOIを採用する可能性は結構高いのではないか、というのが筆者の推定である。問題はその「10nmの先」が本当にあるかであるが、これは回を改めてまた論じたい。

この連載の記事

-

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 - この連載の一覧へ