最新スマホも続々登場! Mobile World Congress 2013レポ 第11回

次のハイエンドスマホに載る!? NVIDIAがTegra 4の概要公開

2013年02月26日 21時00分更新

NVIDIAは、MWC 2013に先立ち、今年1月のInternational CES 2013で発表した「Tegra 4」「Tegra 4i」などの情報を公開した。

さらに機能強化された「Tegra 4」

下位でLTEモデム内蔵の「Tegra 4i」

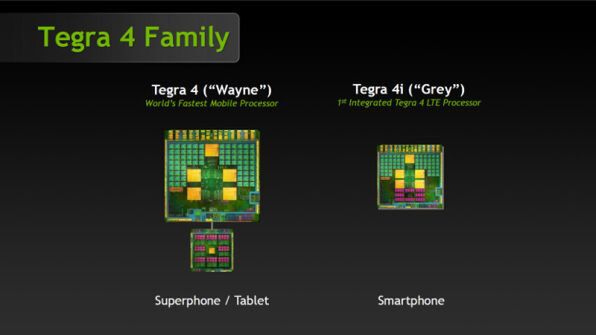

Tegra 4は、CPUコアにARMのCortex-A15を搭載したアプリケーションプロセッサーである。かつて発表されたTegraシリーズのロードマップでは“Wayne”と呼ばれていた。

これに対して、Tegra 4iはCPUにTegra 3と同じCortex-A9を搭載する一方、LTEモデムを統合したモバイル用プロセッサーだ。こちらには、”Gray”というコードネームがつけられているが、2010年に公開されたロードマップには載っていなかったものだ。ただTegra 3のときから、LTEモデムを統合するのではという情報はあった。

Tegra 4は、高性能なA15プロセッサーを4つ搭載し、さらに低消費電力化用のA15プロセッサを持つ「4+1」構成を継承している。この「4+1」構成はTegra 3と同じだ。

前半の4プロセッサー部分は高い性能を持つとともに、SoCとしてビデオや音楽などの再生専用プロセッサーを内部に持つため、メディアの再生中などは、電力消費を抑えることが可能だ。一方、負荷が高くないときは、消費電力の低い5番目のコアが低い周波数、低い電源電圧で動作するため、消費電力を抑えることが可能になっている。

今回、NVIDIAは、低消費電力のデモを行ったが、それはビデオ再生時のもの。スマートフォンではビデオ再生は全画面を使うため、他のプロセスはほとんど止まってしまう。このため、システムの消費電力はかなり小さくなっていた。

Tegra 4/4iともにGPU部分は大幅に強化

また、GPU側が大きく強化されたのもTegra 4シリーズの特徴の1つ。これまで12個だったGPU内部のシェーダーユニット(Tegra 3ではピクセル処理用が8つ、頂点処理用が4つ)を72個(Tegra4)、60個(Tegra4i)にまで増やした。これにより、他社に劣る部分があったグラフィックス性能も大幅に強化した。

Tegra 4iは、LTEモデムを統合し、基板上で占める面積(フットプリント)を大きく削減できる。採用されているプロセッサコアのアーキテクチャは、Tegra 3と同じくCortex-A9だが内部が改良されたR4版を採用したという。

Tegra 3につかわれていたCortex-A9はR2版で、Tegra 4iのR4はTLB(仮想記憶のアドレス変換を高速化する機構)を増量するなどして強化し、さらにプロセスの微細化(Tegra 4シリーズは28nm。Tegra3は40nm)によりクロック周波数を上げ、高速化を達成している。アーキテクチャ、つまりソフトウェア側からみた挙動は同じものの、性能が向上している。また、GPU部分も強化されているため、Tegra 4シリーズとしたのだと考えられる。

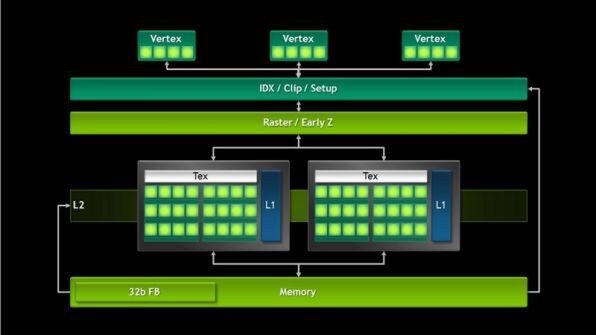

なお、Tegra 4iのGPUのシェーダーユニットの数は60だが、これは頂点処理用のユニットが減らされていて、ピクセル処理用のユニットの数はTegra 4もTegra 4iも同じだという。TegraシリーズのGPUは、レンダリングまでをパイプラインで行なう関係で、メモリから読み出した頂点データは頂点処理ユニットを通ってからピクセルシェーダー(ピクセル処理ユニット)へ入る。

このため、メモリアクセスに十分な帯域がないと、頂点処理ユニットが数多くあってもそれを“埋める”ことができないからだとする。これに対してピクセルシェーダー部分は、ユニット数は同じだが、L1キャッシュを共有するグループが4つ(Tegra 4の場合)から2つに変更されている。L1キャッシュに入れば、ピクセルシェーダーは最大効率で動作できるが、L1キャッシュを埋めるためにはメモリアクセスが必要になるため、メモリ負荷を下げるためにこのような構成になったと思われる。

また、同社は、Tegra4、Tegra4iを使ったスマートフォン用のプロトタイプ基板も公開した。これを見ると、たしかにTegra 4iは、ベースバンド(通信処理を行う部分)がなく、基板上の部品点数も減っている。

Tegra 4は、Tegra 3同様にスマートフォン向け/タブレット向けのSKUがあるということだ。Tegra 3ではスマートフォン用の最大クロック周波数を下げ、最大発熱量を抑えていた。Tegra 4も同様の構成になると思われる。なお、Tegra 4iはフットプリントが重要になるスマートフォンでの利用を想定している。

なお、Tegra 4を採用した端末メーカーはすでに何社かあり、会期中に発表が行われる予定だという。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第26回

スマホ

Nokiaインタビュー 「スマートフォンでは挑戦者 WP8で再起」 -

第25回

スマホ

Android、iOS以外にもチャンスはある 新OS「Jolla」の未来 -

第24回

スマホ

世界と戦う大和魂! MWCに参加の日本ブース -

第23回

スマホ

AppleとGoogleに逆襲開始? MWCで注目の新OSをまとめた -

第22回

スマホ

スマートフォンの性能は今後も確実に向上 ARM社に聞く -

第21回

スマホ

Optimusを武器にスマホの世界トップを目指すLGの戦略 -

第20回

スマホ

Ubuntuスマホは2014年Q1登場予定 「Firefox OSと戦う!」 -

第19回

スマホ

HTCの日本でのブランド認知度を高めたい CPO小寺氏に聞く -

第18回

スマホ

アルミボディーのハイエンド「HTC One」をガッチリ試す! -

第17回

スマホ

MWCの基調講演で感じた、新たな時代のクラスタ化 -

第16回

スマホ

ハイエンドからNexus 4までラインナップが豊富なLG - この連載の一覧へ