インテルCPUの進化を辿る企画。今回は「Merom」こと「Core 2」プロセッサーに搭載された「Coreマイクロアーキテクチャー」について解説しよう。

Yonahをベースに同時4命令実行に対応

Coreマイクロアーキテクチャーは基本的に、前回解説した「Yonah」からの正常進化、という範疇ではあるが、いくつかの要素も変更した結果として、この世代は機能と性能の両面で大幅な進化を遂げている。それもあってか、Yonahまでは特に明確な名前が付けられていなかった内部アーキテクチャーに対して、Coreマイクロアーキテクチャーという名前をわざわざ付けてアピールしている。

これはむしろ「NetBurstアーキテクチャーからの切り替え」を明確にするため、という意味があるのかもしれない。Pentium 4の世代、インテルは内部アーキテクチャーにNetBurstアーキテクチャーという名称を付けてアピールをしていた。この「アーキテクチャー名のアピール」をPentium 4でやり過ぎたがゆえに、Pentium 4から切り替えるにあたって、新しいアーキテクチャー名を強くアピールしないといけなくなったというあたりが、Coreマイクロアーキテクチャーなる名前が表に出てきた理由ではないかという気がする。

実際、Core 2以降は正常進化ということもあって、「Nehalemマイクロアーキテクチャー」や「Sandy Bridgeマイクロアーキテクチャー」といった具合に、インテルは開発モデル名でマイクロアーキテクチャーを紹介しており、こうした名前は付いていないことからもこれが伺える。

それはともかく、YonahからMeromへのアーキテクチャー変更では、以下の3点が主な違いとなる。

- 同時4命令実行にパイプラインを強化

- EM64Tに対応

- Macro Fusion(旧称Macro Ops Fusion)を実装

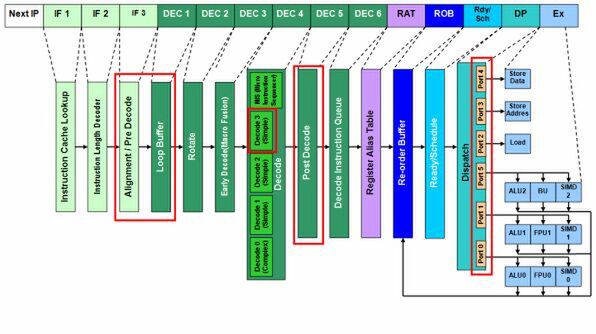

Coreマイクロアーキテクチャー最大の変更点は、同時4命令実行を実現したことだ。これはパイプラインのフロントエンドほぼ全体に影響を及ぼすことになった。「IF1」から「IF3」までのフェッチステージは、おおむねYonahと同じものだ。

ただし、128bit幅のバス(=16byte/サイクル)で1次命令キャッシュから命令をフェッチするところまでは同じだが、そこから取り込むx86命令は、Yonahまでが最大3命令/サイクルだったのが、Meromでは6命令/サイクルに増加している。これは後述するMacro Fusionの効果で、ピーク時には5命令/サイクルで命令のデコードができることに対応したものだ。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ