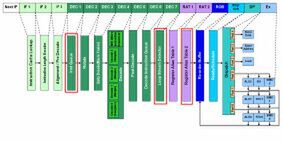

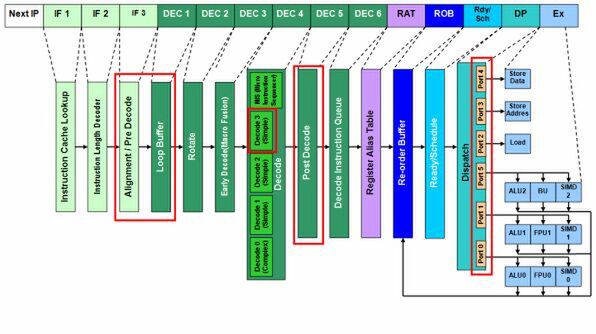

インテルCPUは2006年に投入された「Merom」こと「Core 2」プロセッサーで、内部アーキテクチャーに大きな変更が加えられた。Meromに続いて内部を大きく変更したのが、2008年11月登場の「Nehalem」(初代Core i7)である。今回はCoreアーキテクチャーの原点となったNehalemの特徴について解説しよう。

メモリーコントローラーやGPUを集積したNehalem世代

Nehalem世代の大きな変更点は、以下の3点が挙げられる。

- メモリーコントローラーを含む、いわゆるノースブリッジ機能※1機能をCPU側に集約。

- これにともない、チップセットとの接続が従来のFSBからDMI/QPIに変更。

- 一部モデルではGPUコアもCPU側に集積

※1 インテルの呼び方では、MCH(Memory Controller Hub)/GMCH(Graphics Memory Controller Hub)

もっとも「GPUの集積」については、45nm世代のままでは性能とダイサイズの両面で折り合いが付かなかったようだ。そのため「Clarkdale」というコード名のCore i5/i3(アーキテクチャーはWestmare)では、32nmプロセスで製造したCPUコアと45nmプロセスで製造したGPUコアを、パッケージ内部で接続するMCM(Multi Chip Module)構成といういびつなものになった。結局GPUコアの統合は、次の「Sandy Bridge」まで見送りになってしまった。その意味ではまだ、過渡的なモデルであったと言うこともできる。

CPUコア側での変更点では以下が挙げられる。またMacro Fusionが、64bit命令でも利用できるようになったことが明らかにされている。

- パイプラインステージが16段に増強

- ハイパースレッディング・テクノロジー(HT)を搭載

- 「Power Gating」を搭載

- SSE 4.1/SSE 4.2を搭載

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ