0.13μm SOIプロセスの歩留まりがあがらず苦しむ

AMDはこの時点では明言しなかったが、実は0.13μm SOIプロセスの立ち上げで予想以上に苦慮していた。Yield(歩留まり)もSpeed Yield(どの程度の周波数で動作するかの平均値)もかなり悪かったので、Bartonでは確実を期すために0.13μm SOIの利用を中止した。ただそうなると、Thoroughbredのままでは性能の底上げができないので、2次キャッシュ増量とFSBの高速化で対応したわけだ。

2003年に入ってからも、具体的なラウンチスケジュールは当初まったく聞かれなかった。2002年中にOEM向けにサンプル出荷された初期の「Revision A0」が、「1GHz程度でしか動作しない」という話はそれほど珍しいものではなかった。しかし2003年に入ってリリースされた「Revision B0」でも、2GHzはおろか1GHz台がやっとで、その割には消費電力が多いという話が聞かれるようになる。これではどこまで性能が出るのかと、疑問視されるようになったのがこの頃である。

最終的に「Revision B3」までステッピングを引き上げて、2003年4月22日にAMDは、まずOpteronを発表する(当時の発表記事)。ただしこの時発表されたのは、以下の3製品のみ。だった。

| 名称 | 周波数 | 価格 |

|---|---|---|

| Opteron 244 | 1.8GHz | 9万9250円 |

| Opteron 242 | 1.6GHz | 8万6245円 |

| Opteron 240 | 1.4GHz | 3万5375円 |

発表後には製品も市場に流れるようにはなったが、圧倒的に多いのはOpteron 240で、242とか244はそもそもほとんど流通していなかった。当時Revision B3のSpeed Yieldでは1.4GHzがやっとで、1.6GHzや1.8GHzは高速動作の選別品扱いになっており、これがそのまま価格に反映された。もちろんこんな速度では、デスクトップ向けとしてはPentium 4に及ぶわけがない。

AMDはその後も努力を続け、「Revision C0」でようやく安定して2GHz駆動のClawHammerを出荷できるようになった。これを同年9月23日に「Athlon 64 3200+」としてリリースする。ただRevision C0もあまりゆとりはなかったようで、2004年に投入された「Revision CG」でやっと、「0.13μm SOIで本来想定していた性能」が出たようだ。当初の計画からすると2年ほど遅れたことになる。

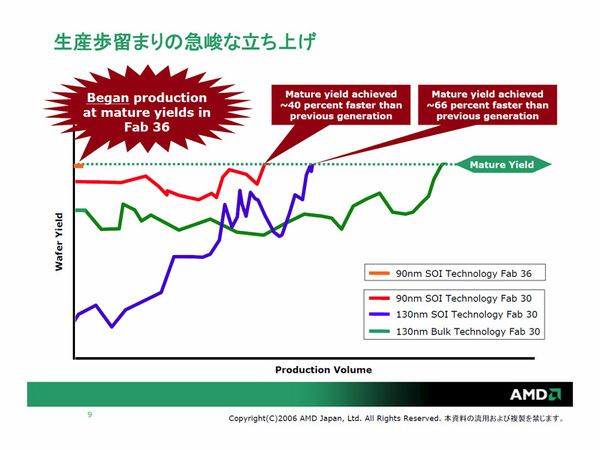

こうした遅れの原因は明白で、0.13μm SOIプロセスの立ち上がりが極端に悪かったのが理由である。2006年に同社の「Fab 36」が90nm SOIプロセスの立ち上がりを紹介した時の資料から、青線で示される「130nm SOI Technology Fab 30」の数字を見れば一目瞭然である。

Mature Yield、つまり「量産出荷を開始するに十分な歩留まり」を達成するまでの時間は0.13μmプロセスよりやや短いが、歩留まりそのものはずっと低かった。恐らく0.13μmプロセスを抜いた、ややぎざぎざの部分がRevision C0あたりで、そこから一度谷になるあたりがRevision CGに切り替えた部分と想像される。これだけプロセスが難航していれば、それは製品が出なくても不思議ではない。

ちなみにこの歩留まりの悪化について、2006年当時に同社のプロセッサー部門製造・技術担当上級副社長を務めていたダリル・オストランダー(Daryl Ostrander)氏に聞いたことがある。オストランダー氏はこれについて、「それまではモトローラ(のHiP7)をベースに製造していたのを、このタイミングでIBM(のCMOS9Sベース)に切り替えた。これは予想以上に困難で、当初の予定よりも長く2年8ヵ月も要した。今から思えばなかなか無茶だったね」と説明した。要するに、当時はここまで切り替えに時間がかかるとは思わなかった、という見通しの甘さがこの遅延の最大の要因だろう。

この遅延によって立ち上がりでもたついたにも関わらず、2004年に投入されたインテルのPrescottが自滅してくれたお陰で(連載118回参照)、Athlon 64やOpteronはそれなりのマーケットシェアを握り、K10コアまで好調に推移することになる。だがもしここで立ち上がりに失敗しなければ、もっと早期にマーケットシェアを握ることが可能だったろうし、AMDの資金繰りもずっと楽になっていただろう。

アーキテクチャーそのものには問題がなかったのは、これに続くK8系列製品が低消費電力・高性能のプロセッサーとして記憶されていることからもよくわかる。とはいえ、0.13μmのバルクCMOSプロセスで製造したCPUが2GHz超えで動いているときに、「30%高速に動作する」はずのSOIプロセスが1.4GHzあたりで苦労しているというのは、明らかにおかしい。やはり、アーキテクチャーの変更とプロセスの変更を同時にやったのが、黒歴史入りの理由ではないかと思う。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ